Get the latest news on developments in the wider community and topics including wireless, embedded and open source silicon.

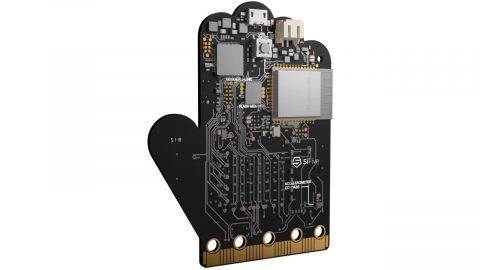

BBC Picks SiFive’s RISC-V-Powered HiFive Inventor for Doctor Who Coding Push

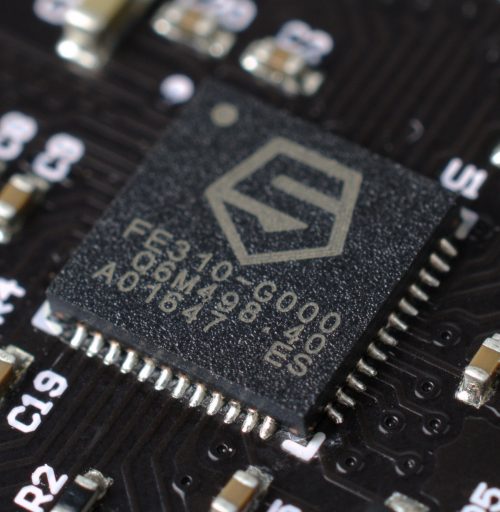

The BBC has announced a partnership with SiFive to bring RISC-V-powered development to kids around the world with the launch of the BBC Doctor Who HiFive Inventor educational development board and supporting coursework bundle. Announced late last year, the SiFive Learn Inventor is a hand-shaped educational development board inspired… Read More