The RISC-V Foundation has released a video highlighting some of the key features of the 2018 RISC-V Summit, held in Santa Clara late last year and attended by over 1,100 community members.

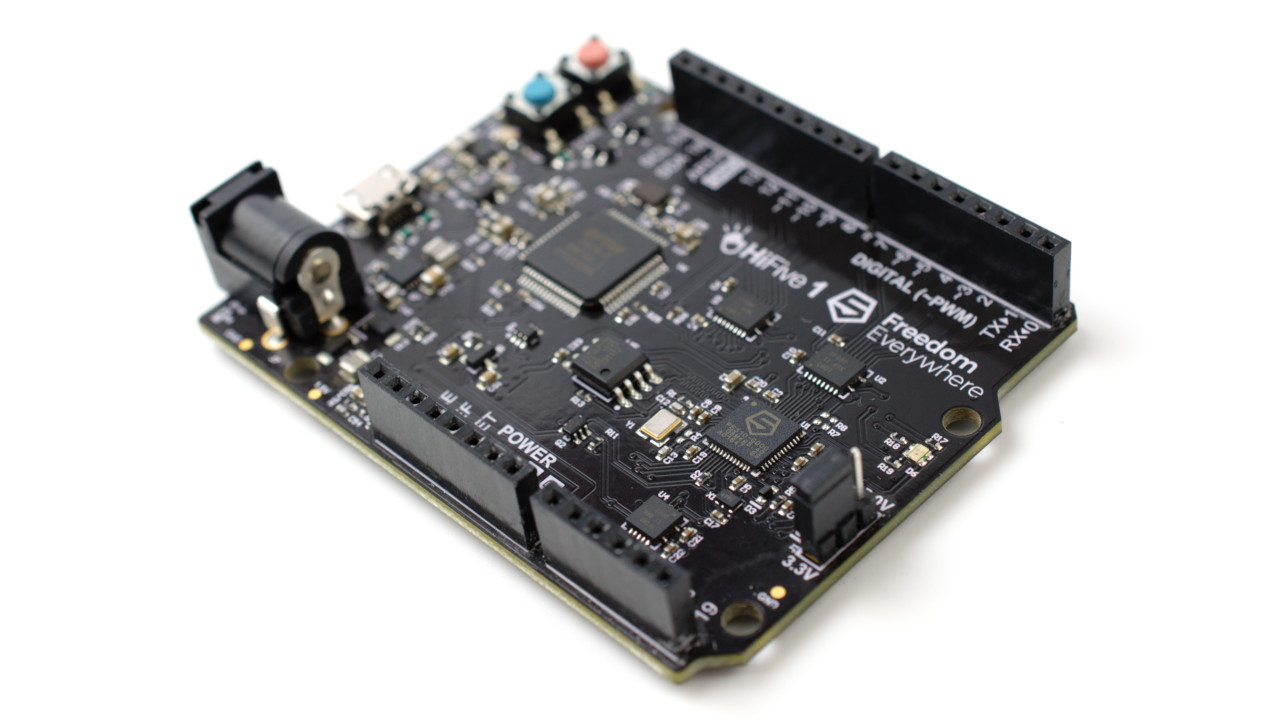

To say that the free and open source silicon (FOSSi) movement in general and RISC-V in particular had a banner year is no exaggeration: in 2018 we saw Ethernet support added to lowRISC, Future ship its first RISC-V FPGA dev board, Esperanto announce its 4,112-core RISC-V AI accelerator, SiFive announce and release the HiFive Unleashed alongside its E7, S7, and U7 RISC-V core families, Greenwaves launch the GAP8 application processor, Fedora release RISC-V disk images, the PULP Platform release PULPissimo, Ariane, and HERO cores, Debian Linux ported to RISC-V, Lime Micro and SiFive announce work on a RISC-V LimeNET base station, the world’s first fully photolithographic homebrew IC, OnChip announce its Itsy-Chipsy fabrication platform and 32-bit RISC-V microcontroller, Rambus’ CryptoManager core, SeL4 for RISC-V, significant progress in OpenPiton project, the SHAKTI project boot outsourced and native RISC-V parts, Zephyr for RISC-V, Mobiveil’s RISC-V programmable storage and Fadu’s SSD controller, Bluespec’s Piccolo and Flute RISC-V cores, the clever Retro-uC, an “overnight” RISC-V implementation, Western Digital’s continued support and evangelism culminating in its SweRV RISC-V core, Buildroot support, desktop Fedora for RISC-V, a RISC-V Soft CPU competition, Eideticom’s P2PDMA support patches, low-cost RISC-V development boards, multi-zone security, the OpenPiton+Ariane collaboration, a free RISC-V VEGAboard for US developers, Microsemi’s PolarFire SoC, a partnership between the RISC-V Foundation and Linux Foundation, Thales’ support for RISC-V and partnership with IIT Madras, the JuxtaPiton project, funding for open-source transprecision computing projects, the surprise announcement that the Raspberry Pi Foundation is to support RISC-V, Wave Computing’s MIPS Open intiative, and a panicked Arm launch, then cancel, an aggressive anti-FOSSi marketing campaign.

In short, it’s been something of a full year – and one to celebrate. In its brief highlight video, the RISC-V Foundation offers those who couldn’t attend December’s event a glimpse of how the community has grown: four days of in-depth presentations from more than 80 experts, 1,100 attendees, and 29 sponsors and exhibitors showing off their wares – including Ashling, Microsemi, Western Digital, SiFive, and SecureRF.

Semiconductor Engineering’s Brian Bailey has published his own piece on the growth of RISC-V, including comment from industry experts including SiFive’s Krste Asanovic and Microsemi’s Ted Speers – and the conclusion that 2019 will be a year of major design wins for the open instruction set architecture.

Beginning with a look at the troubles besetting those clinging to Moore’s Law – the observation turned mandated development target by Intel co-founder Gordon Moore that the number of transistors on a leading-edge part trends toward a doubling roughly every 18 months – and the silicon industry’s search for alternatives, Brian’s piece delves into the growth of RISC-V and predictions for the future.

“With RISC-V, any innovation that happens in the hardware, by collaboration, will create an economic benefit that will be massive,” Microsemi’s Ted Speers, one of the industry experts quoted in the piece, explains. “But who gets rewarded, or how the rewards get funnelled, still has to be figured out.”

“The old model was that you choose a vendor of the core and you get their ISA,” adds SiFive co-founder and RISC-V Foundation chair Krste Asanovic, on the flexibility RISC-V and other free and open source silicon (FOSSi) initiatives bring. “The new model is, ‘I choose RISC-V and then I choose the vendor. I can use a different vendor for every chip, for each product. I can build my own cores. I can use an open source core or a commercial supported core from one of a number of vendors.’”

While Brian’s piece highlights some of the issues the FOSSi movement will have to navigate in the coming years, it ends on an extremely positive note: “2019 will be the year where you will see a lot of high-profile RISC-V design wins,” predicts Codasip’s Chris Jones, “in application areas previously dominated by legacy architectures.”

The LoRa Alliance, which is behind the open LoRaWAN low-power wide-area network protocol designed with the Internet of Things (IoT) in mind, has announced “explosive growth” which has seen it pass more than 100 network operators in around 100 countries.

Designed for minimum power draw and maximum range, LoRaWAN has found a home in the Internet of Things – particularly for community-driven projects like The Things Network, which recently partnered with Digital Catapult UK to deploy the UK’s largest LoRaWAN network and with which AB Open has partnered to launch a Calderdale LoRaWAN network. Now, the success of the open standard is clear: it has been adopted by more than 100 network operators across the globe.

“Reaching this operator milestone is a major achievement for the LoRa Alliance,” says Donna Moore, chief executive and chair of the LoRa Alliance. “Only LoRaWAN has strong, established networks with broad coverage areas, while also offering the private network option. For companies looking to launch IoT products and solutions today, the LoRaWAN standard is the only viable solution. Features like firmware updates over the air and the fact that LoRaWAN is an open specification with a robust certification program ensure network and device interoperability. These benefits give confidence to the market that companies are future-proofed and can deploy solutions today with assurance they will work in the future.”

“This is a huge milestone as it proves LoRaWAN Internet of Things, just as the real internet, doesn’t care about country borders,” adds Wienke Giezeman, chief executive and co-founder of The Things Network. “With The Things Network and The Things Industries we are happy to be present in more than 89 countries and can provide LoRaWAN connectivity in all corners of the world.”

According to figures released by the LoRa Alliance, LoRaWAN networks are showing highest growth in the Asia-Pacific and European regions at a respective 30 and 50 percent last year.

The Khronos Group, best known for its work on the OpenGL and OpenCL graphics and compute language standards, has called for feedback on the potential formation of a working group targeting a new low-level, heterogeneous communications standard for high-performance embedded computing (HPEC).

Targeting markets ranging from the Internet of Things (IoT) to aerospace, industrial, scientific, and medical (ISM), and robotics, the Khronos Group proposes to create an open standard for “markets that wish to focus on algorithm development – not communication intricacies – but need the performance and flexibility of low-level point-to-point protocols with the simplicity of high-level point-to-point methodologies” and with a goal to “unify low-level communication into a simple API with the aim of reducing application complexity, minimising development costs, and accelerating time-to-market.”

Already, the Group has received a design proposal for just such a standard, from Abaco Systems and called the Takyon API. This programming interface, the Group explains, offers just five core functions but brings together low-level point-to-point communication and signalling functionality, with the promise of supporting rapid development of high-performance, scalable, portable, and fault-tolerant applications.

“Khronos has created a methodical exploratory process to enable us to take well-formed proposals for new open standards and evaluate industry interest before we create a working group to develop the standard itself. This process allows us to focus the resources of our members, and of the industry, on efforts that stand an excellent chance of being widely-adopted and having a positive market impact,” explains Neil Trevett, Khronos president, of his organisations call for comments. “We thank Abaco for initiating this investigation, and we look forward to engaging with the embedded industry to gauge the interest in evolving this potential new open standard.”

“Current HPEC communication APIs are typically focused on a particular hardware interconnect/architecture, or a specific thread/process/processor/application locality. Some are very complex, requiring hundreds of lines of code just to handle simple concepts. Others intend to be simple, but get deceptively complex in real-world use cases. Still others mask important, underlying features which can ultimately impact latency and determinism,” claims Peter Thompson, vice president of product marketing at Abaco. “There is no single standard that fits all localities and features – resulting in high development costs, ill-fated shortcuts, and confused embedded HPEC developers. We believe that this effort by Khronos has the potential to address this problem with a simple but elegant API that could become a key open standard.”

More information on Takyon, including an open-source implementation, and the link to provide the Khronos Group with feedback is available on the official website.

Finally, Cocotb, the Coroutine-based Cosimulation TestBench for verifying Verilog or VHDL register-transfer level (RTL) designs using Python, has reached its version 1.1 release – and brings with it the promise of a more rapid and streamlined release schedule for the future.

“This release is the culmination of work done by 50 contributors over a little less than four years,” explains Philipp Wagner of the release. “During that time we merged 242 pull requests, resulting in 257 files changed, with 25,426 insertions and 6,289 deletions recorded by git – growing the codebase by 19,137 lines! So what’s behind all these numbers? A lot of refactorings, bug fixes, and new features!

“You might ask: why did it take so long to get this release out? Cocotb has been maintained by Stu [Hodgson] and Chris [Higgs] since the beginning of (cocotb) time. Cocotb as we know it today exists because of their vision of how to produce a great hardware testing framework. They put a lot of time into developing high-quality code and maintaining cocotb – the popularity of cocotb today is the best indicator of how well that worked out. But as the popularity of cocotb grew, so did the maintenance effort.

“In order to be able to grow further, a team of dedicated volunteers agreed to share the maintainership role with Stu and Chris,” Philipp explains. “Based on a well-documented contribution process we were able to pick up speed again, merging a large number pull requests and giving feedback on many open issues. Today, cocotb development is flourishing with many hard issues being tackled, with documentation being improved, and new features being added. One of the issues being worked on is also a more streamlined release process, making it possible to release more frequently.”

A list of the changes is available in the shortlog, while the release itself can be found on the project GitHub repository.