Microsemi has announced a new system-on-chip (SoC) architecture which combines the company’s PolarFire low-power field-programmable gate arrays (FPGAs) with a complete RISC-V processor implementation for use with Linux platforms.

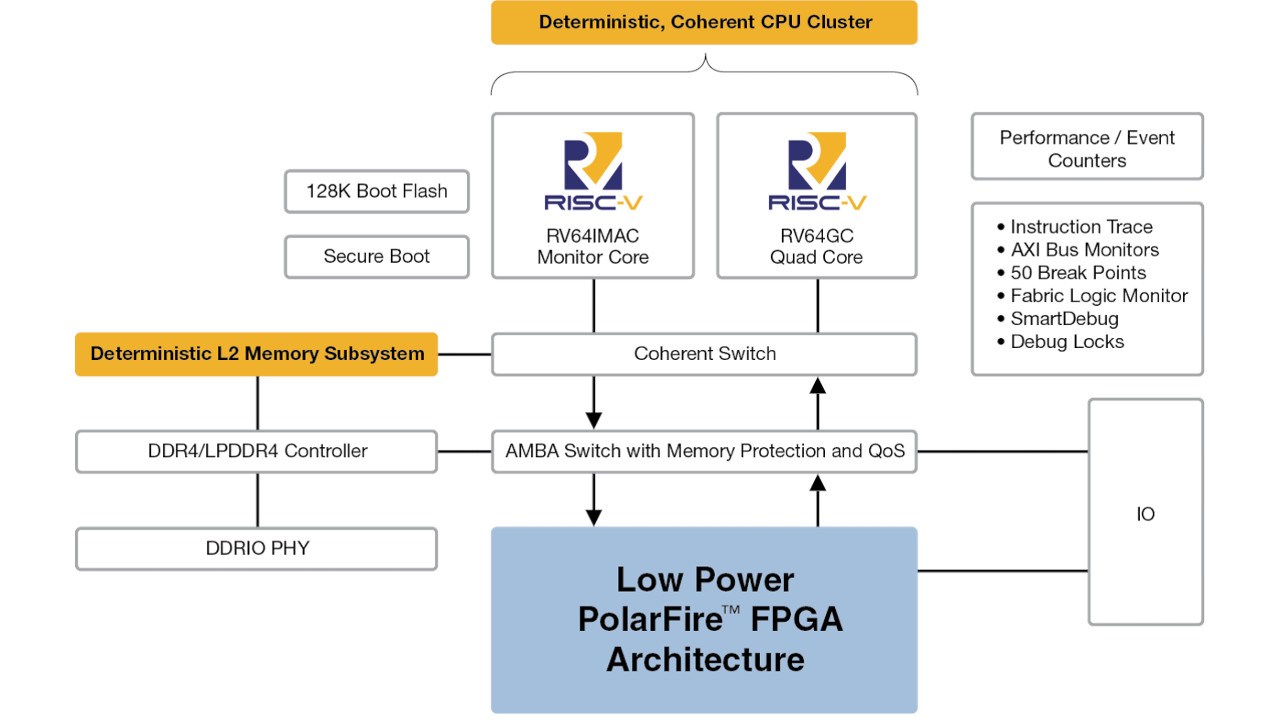

Developed in partnership with RISC-V pioneer SiFive, the PolarFire SoC includes an asymmetric coherent CPU cluster with four 64-bit RV64GC RISC-V cores and one RV64IMAC monitor core, connected to a 2MB Layer 2 memory subsystem via a coherent switch, then on to a DDR4/LPDDR4 memory controller, AMBA switch with memory protection and quality-of-service (QoS) control, and the PolarFire FPGA itself.

“The PolarFire SoC architecture is a compelling combination of low power, security, and reliability in a configurable device that brings real-time to Linux,” explains Bruce Weyer, vice president of the programmable solutions business unit at Microsemi parent Microchip, of the company’s creation. “Coupled with our robust Mi-V RISC-V ecosystem and Microchip’s extensive portfolio of system solutions, the PolarFire SoC architecture gives customers an excellent platform to meet computing’s next great challenges.”

“As a fully customisable, programmable RISC-V platform, the PolarFire SoC architecture gives designers the freedom to create innovative Linux-based SoCs in novel and interesting ways tailored for their distinct, domain-specific requirements,” adds SiFive chief executive Naveed Sherwami. “By leveraging SiFive’s market-leading U54-MC CPU core complex, PolarFire SoC will enable designers to overcome the universal challenge of building real-time systems with predictable behaviours.”

Simulation of the PolarFire SoC is available today via the Antmicro Renode system modelling platform, while a hardware development kit based on SiFive’s HiFive Unleashed is available from Microsemi now. More information is available on the official product page.