The RISC-V Foundation has announced the launch of a design contest, in partnership with Google, Antmicro, and Microchip, which will see entrants competing to build the smallest and fastest RISC-V soft core implementations on field-programmable gate arrays (FPGAs).

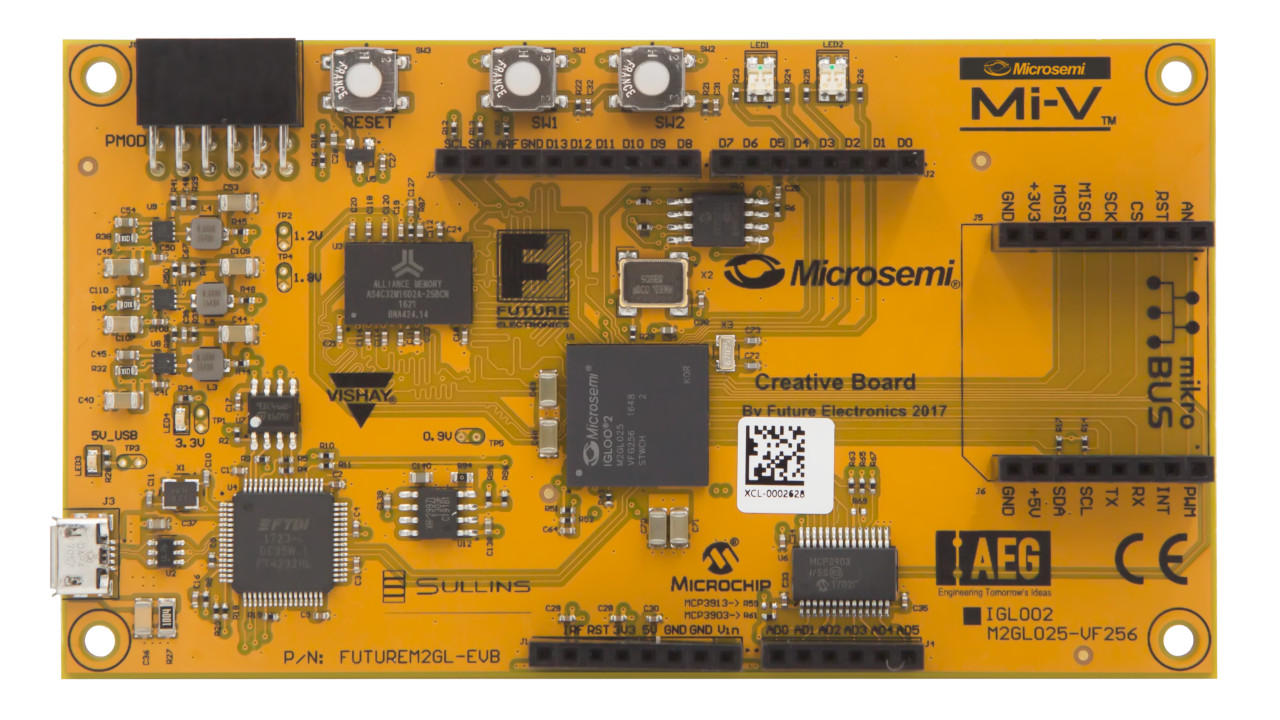

One of the biggest benefits of free and open source silicon (FOSSi) is that you are able to tweak and tailor its design to suit your own needs. To help demonstrate this, the RISC-V Foundation’s design contest is seeking engineers willing to create 32-bit RV32I soft cores and implement them on Microsemi SmartFusion 2, Igloo 2, or Lattice iCE40 UltraPlus FPGA development boards. Each entry will be judged based on two key metrics: size in terms of resource usage, with performance as a tie-breaker; and raw performance in the Dhrystone benchmark.

“As the RISC-V ecosystem has grown, we’ve already seen a wide variety of cutting-edge RISC-V designs in FPGAs as companies and designers take advantage of the free and open model of RISC-V and the flexibility, scalability and extensibility advantages the ISA offers,” explains Rick O’Connor, executive director of the non-profit RISC-V Foundation. “This contest is a great opportunity for designers around the world to experiment with creating ultra-small and high-performance FPGA soft CPU implementations with the RISC-V ISA.”

For engineers on a budget, Microsemi is offering 25 Future Electronics Creative Igloo 2 and 25 Creative SmartFusion 2 FPGA development boards on application, on a first-come first-served basis. The first-prize winner will receive $6,000; second place nets $3,000 plus a Splash Kit and iCE40 UltraPlus MDP development board; third place receives $1,000 plus a PolarFire Evaluation Kit and an iCE40 UltraPlus Breakout Board.

Details of how to enter can be found on the Foundation website, with entries due in by the 26th of November.