Get the latest news on developments in the wider community and topics including wireless, embedded and open source silicon.

Bluespec Launches Commercially-Supported Flute RISC-V Cores

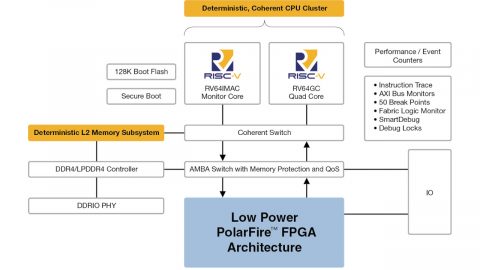

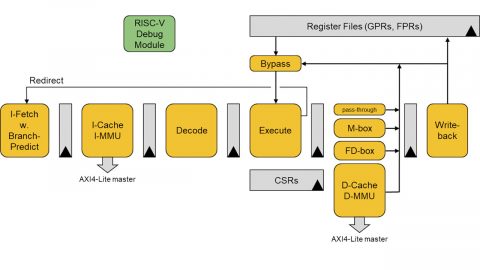

RISC-V specialist Bluespec Inc. has announced its second RISC-V processor design, Flute, which it is making available as basic cores ahead of future releases which will include additional instructions for Linux and FreeRTOS compatibility. The follow-up to Bluespec’s existing Piccolo core, Flute is currently available in RV32IMU and RV64IMASU implementations… Read More