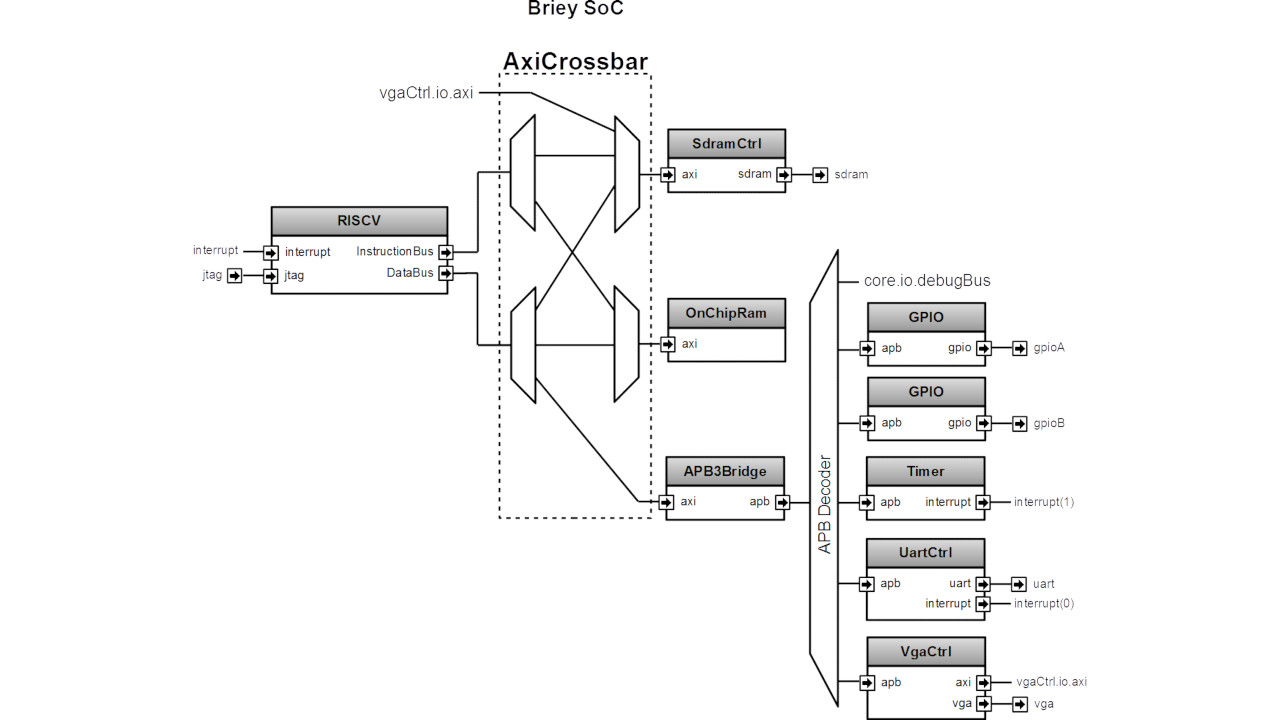

Engineer Tom Verbeure has written up an analysis of the VexRiscV CPU, a RISC-V design implemented using the novel SpinalHDL hardware description language (HDL) – an approach he describes as being “as efficient as the most optimised Verilog, yet at the same time extremely configurable.”

First-prize winner in the recent RISC-V Soft-Core CPU Contest, VexRiscV eschews traditional development methodologies in favour of using the novel SpinalHDL language – a Scala library providing hardware primitives which can be connected together. “You have full flexibility to wire together those hardware primitives anyway you want,” Tom explains. “If you have a configuration that doesn’t need JTAG ports, then you just don’t call the Scala function that creates those IO ports.”

In his analysis of the project, Tom describes VexRiscV as “a complete departure from the traditional way of designing RTL. I found going through the code and figuring out how it all worked fascinating and even entertaining,” he adds. “The VexRiscV is not only amazing in the way its designed, it’s also very high performance for a low amount of resources, with a near infinite amount of configuration options. The difference between a small 0.5 Dhrystone/MHz or a large 1.4 Dhrystone/MHz core is just a few lines of configuration code.”

There are, however, disadvantages to switching from Verilog to SpinalHDL: “The learning curve is very, very steep for a traditional RTL designer,” Tom admits. “That’s mostly because Scala is a rich language, and SpinalHDL/VexRiscV make use of most of this richness. But the biggest [disadvantage] to this system used by the VexRiscV is the fact that the generated Verilog is a flat file. That makes it difficult to debug and understand.”

Tom’s full write-up is available on his blog, along with an earlier general look at SpinalHDL. More information on SpinalHDL and the VexRiscV core, meanwhile, can be found on the project GitHub repository.