OpenISA has officially launched the VEGAboard microcontroller development board, based on the PULP Platform’s RI5CY and Zero-RI5CY RISC-V core, and it’s giving them away to encourage adoption of the free instruction set architecture (ISA).

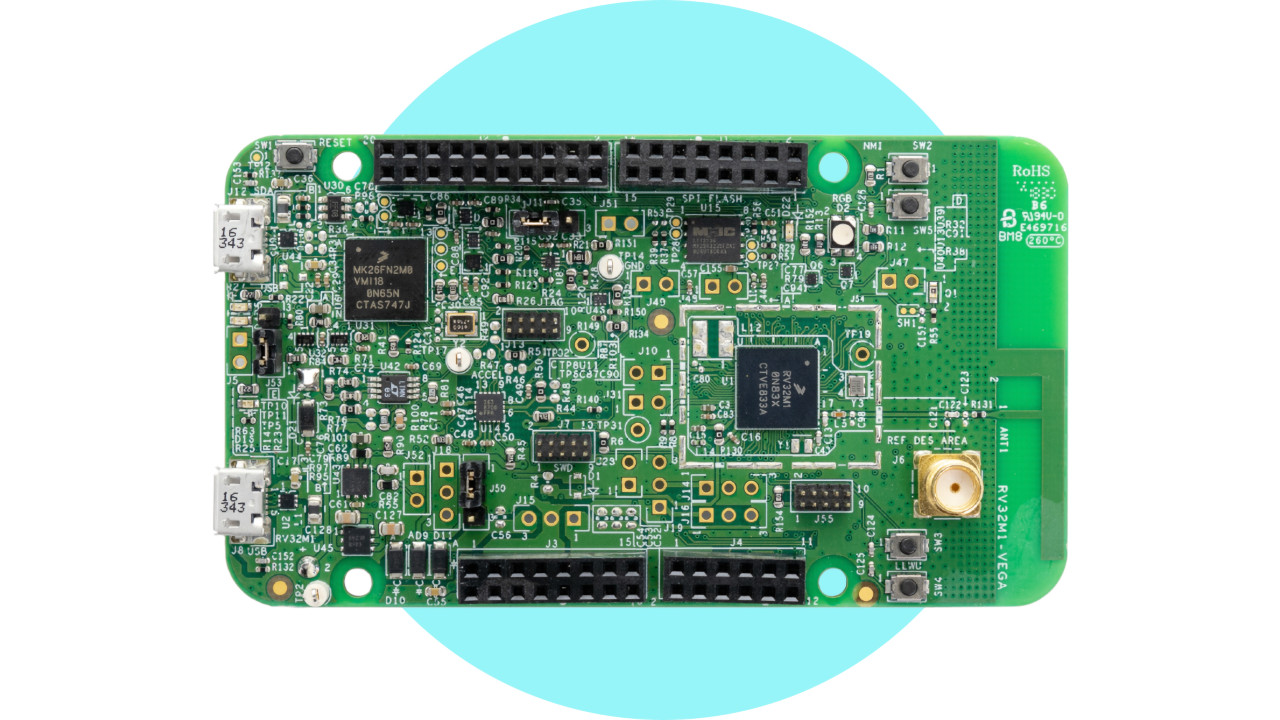

Developed in partnership with the Parallel Ultra Low Power (PULP) Platform, Express Logic, Foundries.io, Ashling, IAR Systems, and Segger, the OpenISA VEGAboard is powered by an NXP Semiconductors RV32M1 chip which combines Arm Cortex-M0 and Cortex-M4 CPUs with RI5CY and Zero-RI5CY cores on a single board. The design also includes an on-board radio with Bluetooth Low Energy (BLE), generic frequency-shift keying (FSK), and IEEE 802.15.4 support, operating in the 2.36-2.48 GHz range.

Each board includes 4MB of serial flash memory, visible light sensor, a digital sensor with accelerometer and magnetometer, an OpenSDA serial and debug adapter, a user-accessible RGB LED, and four push-button switches, along with a printed F-antenna with SMA connector for optional external antenna. Connectivity to external hardware is provided via Arduino-compatible input/output headers.

To encourage RISC-V adoption, OpenISA has announced that it is to give away a limited number of boards free of charge – though, at present, the offer is restricted to the US. Full details, and a link to order a board, can be found on the official website, while documentation and a software development kit is available on GitHub.

Engineer Tom Verbeure has written up an analysis of the VexRiscV CPU, a RISC-V design implemented using the novel SpinalHDL hardware description language (HDL) – an approach he describes as being “as efficient as the most optimised Verilog, yet at the same time extremely configurable.”

First-prize winner in the recent RISC-V Soft-Core CPU Contest, VexRiscV eschews traditional development methodologies in favour of using the novel SpinalHDL language – a Scala library providing hardware primitives which can be connected together. “You have full flexibility to wire together those hardware primitives anyway you want,” Tom explains. “If you have a configuration that doesn’t need JTAG ports, then you just don’t call the Scala function that creates those IO ports.”

In his analysis of the project, Tom describes VexRiscV as “a complete departure from the traditional way of designing RTL. I found going through the code and figuring out how it all worked fascinating and even entertaining,” he adds. “The VexRiscV is not only amazing in the way its designed, it’s also very high performance for a low amount of resources, with a near infinite amount of configuration options. The difference between a small 0.5 Dhrystone/MHz or a large 1.4 Dhrystone/MHz core is just a few lines of configuration code.”

There are, however, disadvantages to switching from Verilog to SpinalHDL: “The learning curve is very, very steep for a traditional RTL designer,” Tom admits. “That’s mostly because Scala is a rich language, and SpinalHDL/VexRiscV make use of most of this richness. But the biggest [disadvantage] to this system used by the VexRiscV is the fact that the generated Verilog is a flat file. That makes it difficult to debug and understand.”

Tom’s full write-up is available on his blog, along with an earlier general look at SpinalHDL. More information on SpinalHDL and the VexRiscV core, meanwhile, can be found on the project GitHub repository.

Western Digital has unveiled its first in-house RISC-V core, dubbed SweRV, and it has confirmed plans to release it under an open source licence early next year.

Part of a company initiative, started in 2017, to switch from proprietary instruction set architectures (ISAs) to the open RISC-V ISA across its storage processing products, Western Digital’s SweRV marks the company’s first public announcement of an in-house processing core. Based on the 32-bit RISC-V variant and designed for manufacturing on a 28nm CMOS process node, the part is claimed to clock up to 1.8GHz and offer performance of 4.9 CoreMarks per megahertz (CoreMarks/MHz).

“As Big Data and Fast Data continues to proliferate, purpose-built technologies are essential for unlocking the true value of data across today’s wide-ranging data-centric applications,” says Western Digital chief technology officer Martin Fink. “Our SweRV Core and the new cache coherency fabric initiative demonstrate the significant possibilities that can be realised by bringing data closer to processing power. These planned contributions to the open-source community and continued commitment of the RISC-V initiative offer exciting potential to accelerate collaborative innovation and data-driven discoveries.”

Interestingly, Western Digital is keeping to the core ethos of the free and open source silicon (FOSSi) movement and plans to release the SweRV core under an as-yet unspecified open-source licence early next year. In the meantime, it has already released a SweRV simulator called Whisper and a cache-coherent memory fabric dubbed OmniXtend.

The OpenPiton project has announced a partnership with the PULP Platform to combine the OpenPiton open-source research processor platform with the 64-bit Ariane RISC-V core, creating what is described as “the ideal permissive open-source RISC-V system.”

The Parallel Ultra Low Power (PULP) Platform announced Ariane, a 64-bit application-class RISC-V design, back in February, while the OpenSPARC-based OpenPiton research processor reached Release 7 in June. Now, with Release 10, OpenPiton is joining forces with PULP to create what the pair are calling OpenPiton+Ariane.

“The Princeton Parallel Group led by David Wentzlaff, and the Digital Circuits and Systems Group of ETH Zürich led by Luca Benini have joined forces to bring you the OpenPiton open-source research processor platform with first-class support for 64-bit Ariane RISC-V cores,” explains OpenPiton’s Jonathan Balkind in the announcement. “The latest update of the open-source Ariane processor, Ariane IV, now supports the P-Mesh cache system from OpenPiton, and with today’s OpenPiton release 10 we have our first working system.

“Going forward, OpenPiton will be the go-to multicore environment for Ariane. Likewise, Ariane will have first-class upstream support in OpenPiton. Together, OpenPiton+Ariane provides the ideal permissive open-source RISC-V system that scales from single-core to many-core.”

Details on simulating the new OpenPiton+Ariane are available on the project’s GitHub repository, while more information on the partnership can be found on the OpenPiton website.

Microsemi has announced a new system-on-chip (SoC) architecture which combines the company’s PolarFire low-power field-programmable gate arrays (FPGAs) with a complete RISC-V processor implementation for use with Linux platforms.

Developed in partnership with RISC-V pioneer SiFive, the PolarFire SoC includes an asymmetric coherent CPU cluster with four 64-bit RV64GC RISC-V cores and one RV64IMAC monitor core, connected to a 2MB Layer 2 memory subsystem via a coherent switch, then on to a DDR4/LPDDR4 memory controller, AMBA switch with memory protection and quality-of-service (QoS) control, and the PolarFire FPGA itself.

“The PolarFire SoC architecture is a compelling combination of low power, security, and reliability in a configurable device that brings real-time to Linux,” explains Bruce Weyer, vice president of the programmable solutions business unit at Microsemi parent Microchip, of the company’s creation. “Coupled with our robust Mi-V RISC-V ecosystem and Microchip’s extensive portfolio of system solutions, the PolarFire SoC architecture gives customers an excellent platform to meet computing’s next great challenges.”

“As a fully customisable, programmable RISC-V platform, the PolarFire SoC architecture gives designers the freedom to create innovative Linux-based SoCs in novel and interesting ways tailored for their distinct, domain-specific requirements,” adds SiFive chief executive Naveed Sherwami. “By leveraging SiFive’s market-leading U54-MC CPU core complex, PolarFire SoC will enable designers to overcome the universal challenge of building real-time systems with predictable behaviours.”

Simulation of the PolarFire SoC is available today via the Antmicro Renode system modelling platform, while a hardware development kit based on SiFive’s HiFive Unleashed is available from Microsemi now. More information is available on the official product page.

Semiconductor Engineering’s Ed Sperling has published extracts of a round-table with Rambus’ Helena Handschuh, Microsemi’s Richard Newell, and Galois’ Joseph Kiniry on the impact the open RISC-V instruction set architecture (ISA) can have on security.

“With open source, you have the opportunity to review it and come up with comments, feed it back to the community, and as a group you can advance maybe not faster but better,” explains Handschuh. “You have more hands. Everybody is available to give you constructive comments, and then you can work together to make it better. That means you start from something that is open and published, and then you evolve it together by adding things and creating white papers.

“We will have [security] issues with RISC-V, as well, and it will be hard to change the hardware. But globally we’re better off because we all learn from each other how to make it better, so that the next time around we can improve. Making things open and public always will help, rather than waiting until someone actually finds a problem and then nobody knows how to fix it.”

“I’m very optimistic for the future,” adds Newell. “We dodged some bullets where RISC-V wasn’t susceptible to attacks like Spectre and Meltdown. But that doesn’t mean it isn’t susceptible to some other kinds of timing analysis attacks. There is a broad range. I have great hope we will be able to develop RISC-V chips without timing analysis vulnerabilities in the future. We have work to do. It will take a few years. But I’m pretty confident we’re going to get there. We’re going to be able to create much more secure chips in the future.”

“The big challenge I see is one of resources,” concludes Kiniry. “We need the right set of expertise. We have working groups set up, with the core set of actors and the right set of expertise in people who have been given the time by their companies to contribute. But we need more people and resources from companies willing to give people a day a week, and we need more resources from government to help out with this.”

The full security-focused extract can be found on Semiconductor Engineering now.

Finally, the Linux Foundation has announced that it is bringing the Joint Development Foundation under its wing, in order to bring together open source and open standards development and simplify the route to standardisation for developers.

The partnership between the two organisations will, they claim, benefit both individual open-source developers and corporate contributors as well as end users. Any Linux Foundation project will be free to use the Joint Development Foundation’s standard development model alongside the Linux Foundation’s agreements with other, external, standards organisations.

“Linux Foundation communities have been engaged in developing open standards and specifications around Linux since day one, and more recently with newer efforts such as OpenChain and the Open Container Initiative, to collectively solve technical challenges,” explains Jim Zemlin, Linux Foundation executive director. “Leveraging the capabilities of the Joint Development Foundation will enable us to provide open source projects with another path to standardisation, driving greater industry adoption of standards and specifications to speed adoption.”

“We are excited to join the Linux Foundation to support the development of specifications and standards with the resources and scale that the Linux Foundation brings to its projects,” adds David Rudin, president of the Joint Development Foundation. “The Joint Development Foundation has brought together diverse communities to develop specifications and source code. We’re looking forward to working with the Linux Foundation, its projects and external standards organisations as we continue to foster new JDF standards.”

Existing Joint Development Foundation projects include the Alliance for Open Media, Decentralised Identity Foundation, Internet of Learning Consortium, and 3MF, while the non-profit organisation has grown to over 100 members since its formation in 2015.