It’s been a busy fortnight for the open silicon, starting with the news that the RISC-V Foundation, the driving force behind the eponymous open processor architecture, has announced the formation of a security standing committee – and is asking for cooperation from the broader industry.

“As the number of connected devices grows exponentially and new security vulnerabilities like Meltdown and Spectre emerge, it’s become increasingly important to develop more robust security approaches. The RISC-V community has the historic opportunity to leverage a new platform for security innovation, leveraging the latest knowledge and contributions from leading industry and academic experts that comprise the expansive RISC-V ecosystem,” explains Rick O’Connor, executive director of the non-profit RISC-V Foundation, of his organisations decision to launch the committee.

“The RISC-V Foundation’s Security Standing Committee is a declaration and call to action for industry leaders, universities and government organizations to join the Foundation and work with us to build a more secure world for the benefit of everyone.”

“Security is one of the fundamental issues in our connected world. The RISC-V community is committed to pushing the industry forward through innovative approaches and new thinking to address existing and emerging threats,” adds Dr. Helena Handschuh, chair of the RISC-V Foundation Security Standing Committee and fellow at Rambus. “Through open standard collaboration, the Security Standing Committee is fostering the growth of the RISC-V ISA to ensure it meets and exceeds the dynamic security demands of this new era of innovation.”

More information on the RISC-V Security Standing Committee is available on the official website.

OnChip has promised to launch a call for participation in its Itsy-Chipsy low-cost semiconductor manufacturing facility, and is already receiving interesting suggestions from potential users.

Announced back in April, Itsy-Chipsy aims to allow smaller companies and hobbyists to produce application-specific integrated circuits (ASICs) for as little as $100 by providing a chip platform with utility blocks placed on a chip to service custom blocks designed by the platform’s users – the equivalent, the company explains, of popular low-cost PCB manufacturing facility OSH Park for silicon.

Now, the company is seeking potential projects to test the platform – and has already received interest in producing a small but fully free and open source implementation of a field-programmable gate array (FPGA), which it describes as “doable” on Itsy-Chipsy’s current incarnation.

The company has also released a project update via its Hackaday.io page, detailing a visit to semiconductor facilities in Taiwan to resolve the potential issues of “non-disclosure agreement (NDA) aggregation” in which every maker contributing a design to be produced will need to sign an NDA – something the company claims it may have resolved through the adoption of a “more relaxed NDA,” at least for digital blocks.

OnChip has yet to announce a go-live date for its public Itsy-Chipsy tests.

The growing impetus behind the free and open source silicon (FOSSi) RISC-V project appears to have industry incumbents rattled, with Arm launching then rapidly removing an aggressive marketing campaign which attempts to sow the seeds of doubt in engineers’ minds about the ISA’s benefits versus Arm’s own proprietary intellectual property (IP).

Following the launch of affordable RISC-V ASICs from companies including SiFive and the news that Nvidia, Rambus, and Western Digital are all shipping or planning to ship products featuring RISC-V cores, it’s fair to say the the FOSSi project is enjoying considerable success. Cambridge-based Arm, though, is watching with something other than pleasure: seeing a threat to its majority share of the embedded and low-power microprocessor markets, the company has responded with an aggressive and arguably misleading marketing campaign.

In its riscv-basics.com website, since pulled down following considerably industry outcry, Arm lays out five claims – cost, ecosystem, fragmentation, security, and design assurance – in which it claims its proprietary IP wins out against the open RISC-V ISA. Its claims, though, are not backed by any publicly-available data, and in many cases appear to be based on little more than marketing puffery.

In true hacker style, Arm’s site has competition: arm-basics.com, a domain it’s hard to believe Arm didn’t think to register before launching its campaign, offers counterpoints to Arm’s marketing spiel and – in-keeping with the RISC-V ethos – is open-source with contributions welcome on its GitHub repository.

Renode, Antmicro’s virtual development tool for multinode embedded networks, has received support for SiFive’s Freedom E310 and HiFive Unleashed development boards.

“Renode was created based on many years of experience with the development of software for embedded systems – both for gateways, on-board computers as well as sensor nodes and microcontrollers. Testing and developing physical embedded systems is difficult due to poor reproducibility and lack of insight into the current state of a system, especially in multinode scenarios,” Antmicro explains of the tool’s reason for being. “Renode addresses this issue by letting you run unmodified binaries, identical to the ones that you would normally flash onto their target hardware, on a virtual board or system of boards.

“One important aspect of the tool is that it simulates not only CPUs but entire SoCs (including e.g. heterogeneous multicore SoCs and various peripherals) as well as the wired or wireless connections between them, which allows users to address complex scenarios and test real production software.”

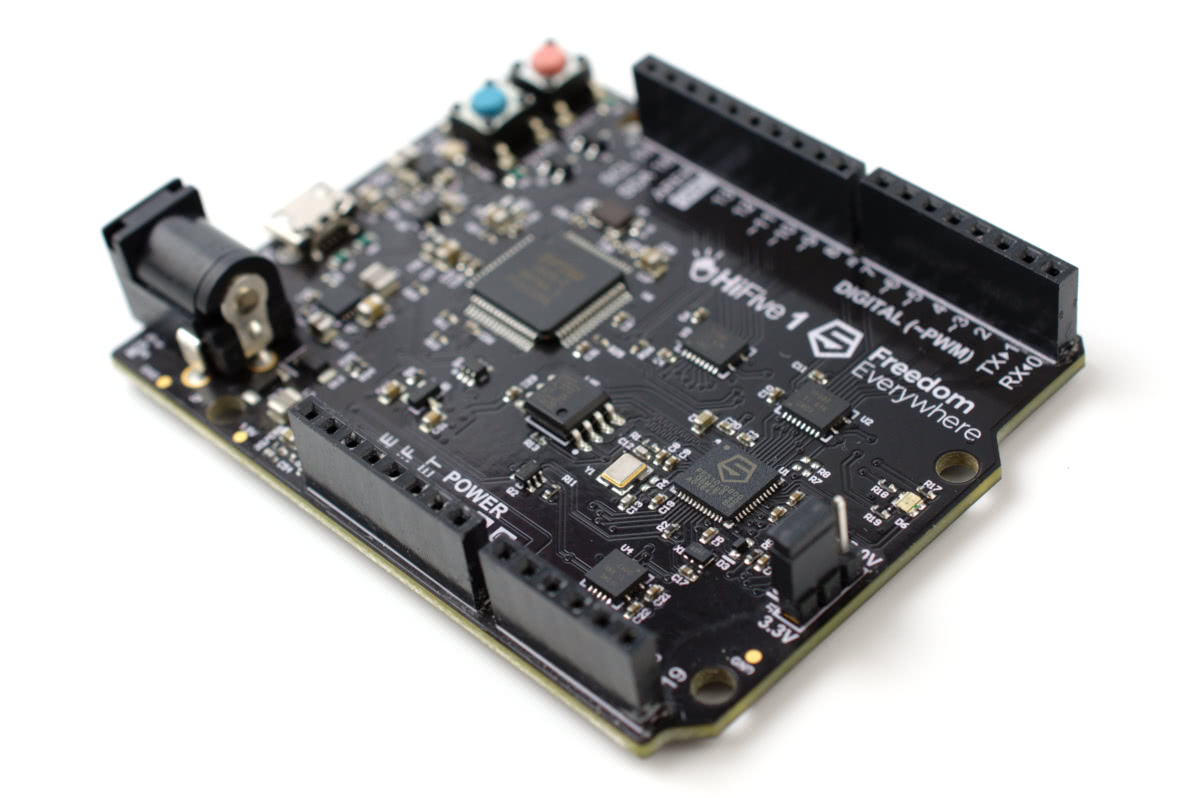

The latest release of the tool, Renode 1.4, brings new support for SiFive’s Freedom E310 RISC-V platform and its Linux-targeted HiFive Unleashed 64-bit RISC-V development board, covered in detail in our getting started guide. The new release also includes generic 64-bit RISC-V target emulation, support for 64-bit registers, initial support for EFM32, EFR32, and EZR32 microcontrollers from SiLabs, and numerous improvements and bug fixes.

More information, and the binary and source downloads, are available on the project’s GitHub repository.

Those interested in experimenting with the LoRaWAN long-range low-power standard now have a new resource, in the form of an introductory tutorial by Nick Poole published on SparkFun.

Based around SparkFun’s own SparkX Pro RF USB-connected development board, Nick’s detailed tutorial introduces the LoRa and LoRaWAN standards, The Things Network community-driven LoRaWAN network project, and the concepts behind how a LoRaWAN network operates before going hands-on with the development board and connecting it to The Things Network.

“Services are based on best effort,” Nick writes of The Things Network, “so there’s no guarantee on uptime or latency, but it’s free! The Things Network also encourages members to grow the network by making it incredibly easy to register a gateway. Simply connect your gateway hardware to the Internet, open the TTN console, and follow the prompts.

While Nick’s tutorial requires that you are within range of a The Things Network gateway, it links out to additional tutorials on using the official TTN gateway hardware, a Raspberry Pi, or even a low-cost ESP8266 to create a TTN gateway – handily extending the network’s coverage to currently unserved areas.

The full tutorial is available now on SparkFun’s education site.

Finally, Standard IEEE 1934, the Institute of Electrical and Electronics Engineers’ first standard for so-called “fog computing,” has officially received a reference architecture: OpenFog.

Sitting somewhere beyond cloud computing, fog computing is a horizontal architecture designed to distribute resources – from computing power to storage – anywhere between the clouds at the top and embedded devices at the bottom. The OpenFog Consortium, founded two years ago, has been working to develop standards for fog computing – and has now been validated in the form of IEEE 1934.

“We now have an industry-backed and -supported blueprint that will supercharge the development of new applications and business models made possible through fog computing,” claims Helder Antunes, chair of the OpenFog Consortium and senior director at Cisco, of OpenFog’s adoption in the IEEE 1934 standard. “This is a significant milestone for OpenFog and a monumental inflection point for those companies and industries that will benefit from the ensuing innovation and market growth made possible by the standard.”

“The reference architecture provided a solid, high-level foundation for the development of fog computing standards,” adds John Zao, chair of the IEEE Standards Working Group on Fog Computing & Networking Architecture Framework. “The OpenFog technical committee and the IEEE standards committee worked closely during this process and benefited from the collaboration and synergies that developed. We’re very pleased with the results of this standards effort.”

More information on OpenFog can be found on the official website, while IEEE 1934 has been published as a draft standard by the IEEE Standards Association (IEEE-SA).