Wave Computing has announced the MIPS Open initiative, under which it plans to make the instruction set architecture (ISA) available free of charge with no licensing or royalty payments required – a clear response to the growing popularity of the open RISC-V ISA.

Wave Computing, which acquired MIPS from Imagination Technologies in June last year, has confirmed that MIPS Open will allow both 32-bit and 64-bit variants of the MIPS ISA to be adopted for research and commercial use with no licensing fee or royalty payments, including full licences to the company’s MIPS-related patent portfolio.

“Having spent years in the open source technology movement, I can attest to the hunger for community-driven solutions,” claims Art Swift, president of Wave Computing’s MIPS IP arm. “However, until now, there has been a lack of open source access to true industry-standard, patent-protected, and silicon-proven RISC architectures. The overwhelmingly positive response we have received thus far from customers on our MIPS Open initiative is an indication of the dramatic, positive impact we believe the program will have on the industry. We invite the worldwide community to join us in this exciting journey and look forward to seeing the many MIPS-based innovations that result.”

“The MIPS Open initiative is a key part of Wave’s ‘AI for All’ vision,” adds Lee Flanagin, Wave’s senior vice president and chief business officer. “The MIPS-based solutions developed under MIPS Open will complement our existing and future MIPS IP cores that Wave will continue to create and license globally as part of our overall portfolio of systems, solutions, and IP. This will ensure current and new MIPS customers will have a broad array of solutions from which to choose for their SoC designs, and will also have access to a vibrant MIPS development community and ecosystem.”

Detail on exactly how the MIPS Open IP will be licensed, however, is not set to be confirmed until the first quarter of 2019 – and it’s not yet clear whether Wave is taking the free-as-in-beer approach recently adopted by Arm in response to RISC-V’s growing popularity or a full free-as-in-speech open-source release that would make MIPS a true competitor to RISC-V.

Thales, which recently became a member of the RISC-V Foundation, has announced a joint project with IIT Madras to develop a fault-tolerant version of the SHAKTI Project RISC-V CPU.

“After the two successful fabrication and booting of SHAKTI with two technology nodes, 22nm (Intel Fab, Oregon USA) and 180nm (SCL Chandigarh fab, India), this tie-up with Thales is very exciting and certainly is a big step towards taking SHAKTI family to the global technology ecosystem,” claims Professor Kamakoti Veezhinathan of the Reconfigurable Intelligent Systems Engineering (RISE) Laboratory at IIT Madras. “With the advent of more and more safety critical systems adopting electronics hardware for intricate control and monitoring, fault-tolerance and security features are of prime importance in next generation processors. This tie-up with Thales, I am sure, will result in a detailed analysis of these features resulting in a framework that could be adopted for designing the next generation Shakti-based safety-critical systems.”

“By adopting an open approach to both hardware and software, this joint effort will create new opportunities for the design of mission-critical systems in all sectors, including aerospace, space, transportation, security and defence,” adds Thales Research and Technology R&D computing manager Arnaud Samama. “With this, we look forward to taking our partnership, which was formed in March this year, to the next level.”

The SHAKTI Project recently celebrated booting Linux on the first CPU to be fabricated in India, while an interview with Arjun Menon and Rahul Bodduna on the project’s progress as of ORConf 2015 is available as part of the AB Open Open Source Digital Design Insights (OSDDI) video series.

RISC-V specialist Bluespec Inc. has announced its second RISC-V processor design, Flute, which it is making available as basic cores ahead of future releases which will include additional instructions for Linux and FreeRTOS compatibility.

The follow-up to Bluespec’s existing Piccolo core, Flute is currently available in RV32IMU and RV64IMASU implementations with a floating-point and compressed-instruction variant supporting Linux and FreeRTOS operating systems to follow. The core uses a five-stage pipeline, can run at 100MHz on the Xilinx UltraScale field-programmable gate array (FPGA) platform using fewer than 5,000 look-up tables (LUTs), with 4KB instruction and data cashes and hardware multiply-divide.

“The availability of commercially-backed open-source processor cores is a unique RISC-V value proposition,” claims Rick O’Connor, executive director of the RISC-V Foundation, of Bluespec’s release. “With the emergence of the free and open RISC-V ISA an open-source business model is now possible for processor IP. This will certainly help RISC-V ignite a new era of hardware innovation, as Linux did for software.”

While only recently made available publicly, the Flute core has already found real-world uses: “We are using Bluespec’s Flute core as a fast and efficient way to take to market our Posit Numeric Unit IP,” explains Anantha Kinnal, co-founder and director of Calligo Technologies, an HPC and AI company based in Bangalore, India. “It provides us customization opportunities, an ability to focus on our value-added technology, and confidence to go to market with the necessary commercial support.”

The Flute core is available to download now in 32-bit and 64-bit variants, with Verilator and Icarus simulations, upon submission of the registration form on the official website.

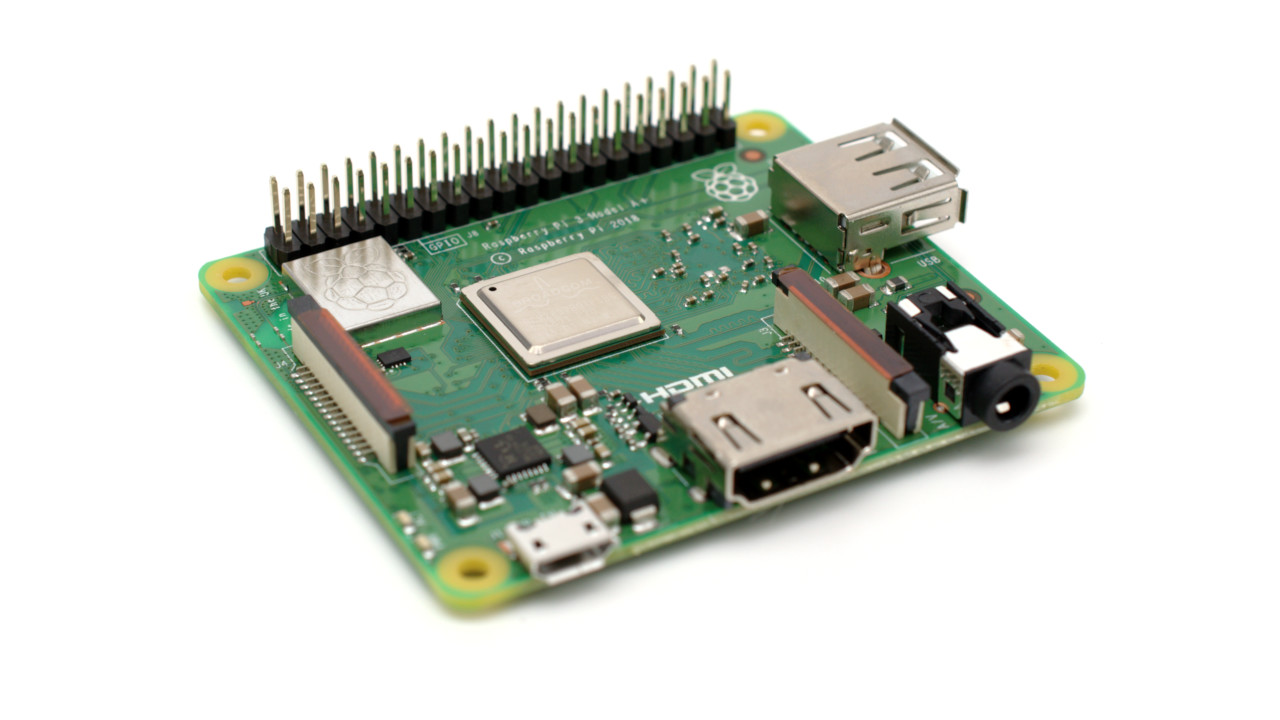

The Raspberry Pi Foundation has announced its membership of the RISC-V Foundation at the Silver Member tier, offering support for the instruction set architecture on a software – though not yet hardware – level.

The original Raspberry Pi launched in February 2012 as a low-cost single-board computer (SBC) primarily targeting the hobbyist and educational market and based around a Broadcom BCM2835 single-core Arm system-on-chip. Originally developed for set-top box use, the Broadcom chip boasted surprisingly powerful graphics but a weak, 32-bit processing core – something the not-for-profit Raspberry Pi Foundation has sought to address in more recent releases, eventually settling on a 64-bit quad-core Arm Cortex-A53 IP.

Now, though, the Foundation has announced that it is joining the RISC-V Foundation, suggesting that a shift away from Arm could be on the cards. “We’re excited to have joined the RISC-V Foundation as a silver member,” the Raspberry Pi Foundation posted to its Twitter account. “[We’re] hoping to contribute to maturing the Linux kernel and Debian port for the world’s leading free and open instruction set architecture.”

A shift from the proprietary Arm architecture to RISC-V would fit in nicely with the Foundation’s goal of low-cost, highly-accessible computing for education and industry – but would put paid to its tradition of keeping backwards compatibility where possible, something it has already suggested might be the case when it moves away from the Broadcom BCM283x platform for the Raspberry Pi 4. Foundation co-founder Eben Upton, though, is clear: the Foundation is currently focusing on supporting the ISA in software, and not with a development board launch.

“This isn’t a product announcement,” explains Eben. “We believe that instruction-set diversity is important, that open, free instruction set architectures are an important enabler for innovation, and there’s a lot of exciting work going on in the RISC-V community at the moment.

“Our impression is that the hardware side of things is going pretty well. We think we can contribute on the software side, which is important if RISC-V is going to become a viable alternative for desktop general-purpose computing. By ‘software,’ we mean some subset of toolchain, kernel, userland, SIMD fastpaths, JITs, etc. We will be soliciting proposals for small projects in these areas.”

More information, including how to contribute a proposal, will be available on the Raspberry Pi Blog in the near future, Eben confirms.

Engineers working on field-programmable gate array (FPGA) projects and looking for a friendly development environment to add to their toolchain now have a new option: the VerilogCreator plugin for QtCreator.

Written by Rochus Keller and brought to our attention by Hackaday, VerilogCreator is designed to turn the QtCreator integrated development environment (IDE) into one suitable for working on Verilog 2005 projects, complete with syntax highlighting, code warnings and errors, jump-to drop-down options, code folding, and the ability to directly run compilers and simulators within QtCreator or to generate command files for Verilator and Yosys.

“The plugin is still work in progress, but it already has enough functionality to analyse existing code bases or to develop new code,” Rochus explains of his project. “The current version supports Verilog 2005 syntax checking/colouring and semantic code navigation/highlighting; there are build configurations for Icarus, Verilator, Yosys and Tcl. Projects can be configured using a file format similar to qmake.

“Even though I’m using Qt for twenty years and QtCreator for ten years this is my first noteworthy QtCreator plugin,” Rochus continues, explaining that issues surrounding poor quality and outdated documentation made the process considerably more difficult than expected. “All in all it is now clear to me why there are comparatively few plugins for QtCreator in all these years and most of them come directly from the Qt Company,” he adds in explanation for why the plugin only supports QtCreator 3 and not QtCreator 4. “Source and binary compatibility between QtCreator versions is not only complex, but a full-blown nightmare.”

The full plugin, which is licensed under the GNU General Public Licence, is available on GitHub.

The KiCad community is to get its first-ever dedicated conference this year, in the form of KiCon 2019 which is to be held this April in Chicago, USA.

Designed to bring together both users and developers of the open-source KiCad electronic design automation (EDA) software suite, KiCon 2019 has been announced by organiser Analog Life. While a selection of speakers have already been confirmed – including KiCad project lead Wayne Stambough and developer Maciej ‘Orson’ Sumiński, Great Scott Gadgets’ Michael Ossman, KiCost, KiField, and SKiDL creator Dave Vandenbout, and event organiser Chris Gammel – additional presentations, talks, and workshops are being welcomed.

“We are looking for community members to propose talks, which will be recorded and uploaded for the rest of the world to utilise,” writes Chris Gammel. “We’re looking for stories about tools, methods, and successes using KiCad in manufacturing, research and business. This conference will bring together the power users of the tool to talk about how they use KiCad on a regular basis and to share that knowledge with others.

“This conference stemmed from a growing online community of KiCad users,” Chris continues. “This conference is a first attempt at getting those online denizens all in one place at one time. FOSDEM is a gathering of open source software developers and is a great place to learn more about how to contribute to the KiCad project as a software developer; these developers are a key piece to the advancement of the project. Each year Wayne Stambaugh gives a ‘State of KiCad’ talk that is delivered to a packed room. However, the focus there is on the development of KiCad, not the every day use of KiCad. This conference is to focus on KiCad users and advancing the state of the art of using open source tools for hardware development.”

The inaugural KiCon is scheduled for the 26th and 27th of April 2019 in Chicago’s mHUB. More information, for those interested in attending as well as those looking to propose a talk or workshop, can be found on the official website.

Tidelift, a company founded by former Red Hat staff which aims to provide sustainable funding to open source projects, has announced a $25 million Series B funding round – on top of $15 million it raised last year.

“Tidelift makes it possible for open source creators to get paid for doing the work they love,” explains co-founder Donald Fischer of his company. “By delivering the support and assurances that professional teams who use their software need, creators can get a new source of income to support their work. In September we opened the doors for any open source project to sign up to participate in Tidelift, surpassing $1 million in guaranteed income for many projects in the JavaScript, Java, Python, Ruby, and PHP communities.

“In the few months since that announcement, open source creators—both individuals and teams—who collectively maintain thousands of open source packages including Apache Struts, Nokogiri, Mongoose, Setuptools, Project Lombok, Joda-Time, Pillow, PromiseKit, and Beautiful Soup, have joined alongside the maintainers of projects like Vue, Material-UI, Babel, Gulp, Fabric, Active Admin, Doctrine, and StandardJS to participate in Tidelift. More than 35 million open source repositories now depend on packages that are included in the Tidelift Subscription.”

The Tidelift platform works in a similar way to Medium’s subscription-based publication model: Users of open-source packages are invited to pay a subscription fee to Tidelift, which is then shared out amongst the maintainers of the packages they use. In exchange, subscribers receive a dashboard which provides security alerts, licence compliance monitoring, maintenance alerts, and direct access to quality-controlled security updates.

“Open source doesn’t just need ‘funding.’ It needs a better business model that works for creators and users alike, at massive scale,” claims Donald. “This investment in Tidelift enables us to make that business model possible. We’re thrilled to have the support of investors who are fully aligned with our commitment to the open source community, business strategy, long-term vision, and values.”

More information is available from the company’s official announcement.

Finally, Design News’ Chris Wiltz has predicted that 2019 will be “the year of open source,” and while it’s hard to imagine the impact of open source software getting any greater than it already has it’s clear that the impetus behind open hardware is growing at an exponential pace.

In the piece, which begins as a retrospective of the big moves in the world of free and open source software (FOSS) and open hardware throughout 2018, Chris points to what appears to have been an inflection point for open hardware, and in particular free and open source silicon (FOSSi) projects. “Building custom silicon chips—a notion once far too impractical and costly for all but the largest chipmakers—is now a serious reality,” he writes, “thanks to RISC-V, an open-source instruction set for building chip architectures.”

Chris points to a range of developments from companies including SiFive, Microsemi, Western Digital, and Esperanto, though skips over some of the impressive efforts of others including IIT Madras, Thales, OpenISA, PULP Platform and OpenPiton, Bluespec, Huami, Sipeed, Hex Five, lowRISC, and even the not-for-profit Raspberry Pi Foundation, all of whom have released or announced RISC-V-based projects over the last year.

The piece concludes with some warnings, however, with a particular focus on embedded efforts. “Paramount among issues encountered by developers using open source were incomplete or confusing documentation and a lack of responsiveness and support from developers,” Chris explains. “Among those surveyed by GitHub, 93 percent said there is a ‘pervasive problem’ in the open-source community with incomplete or outdated documentation.”

The full piece is available now on Design News.