Storage giant Western Digital has published full instructions for building the Gnome Desktop variant of the Fedora Linux distribution for RISC-V, targeting the SiFive HiFive Unleashed development board.

As part of Western Digital’s push to ship more than a billion RISC-V cores per year, as it moves away from proprietary architectures for its storage processing products, the company has been working heavily on development surrounding the open instruction set architecture. As part of that, engineer Atish Patra has published full instructions for building a RISC-V desktop – complete with the software you’d need for general-purpose use.

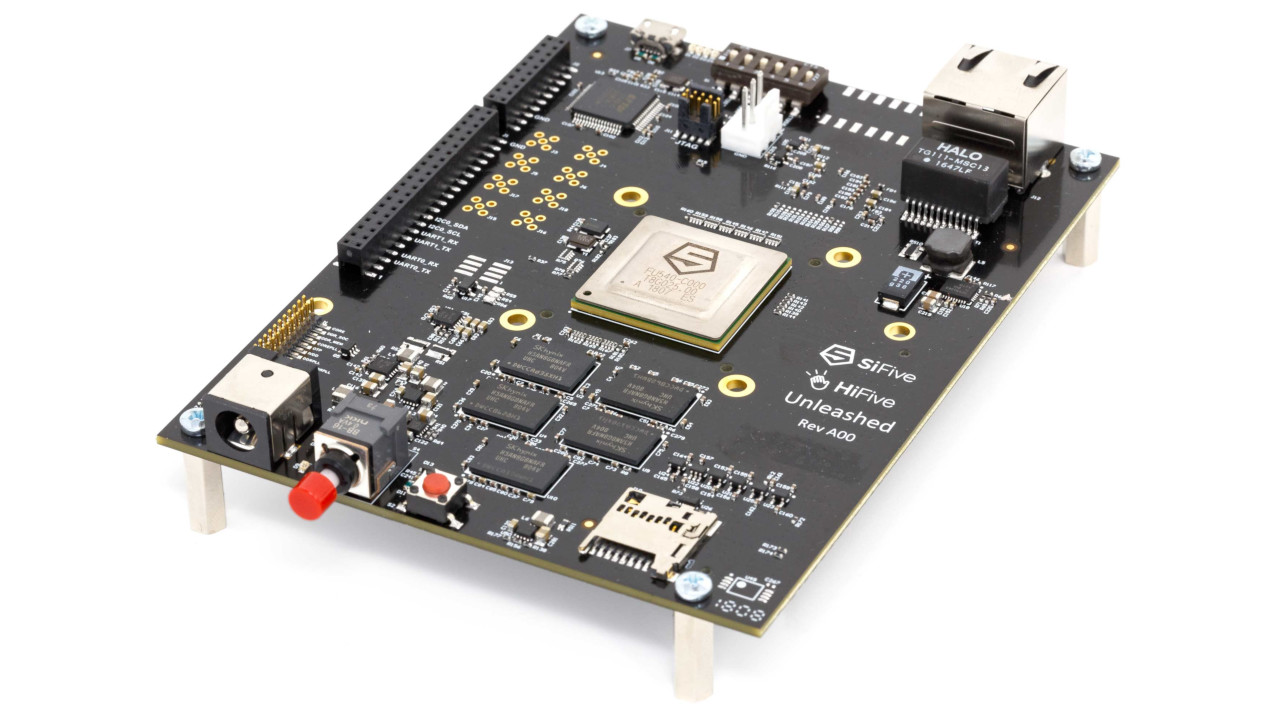

While based on the HiFive Unleashed development board, there is a reasonable list of additional hardware required to add storage and graphics capabilities: as well as the HiFive Unleashed itself, anyone wanting to duplicate WD’s approach will need the Microsemi HiFive Unleashed Expansion Board, a Radeon HD 6450 or similar Caicos-based graphics card, PCIe USB card for a keyboard and mouse, and SATA or NVMe storage for the operating system itself.

Atish’s full instructions, along with supporting software required for the build process, can be found on Western Digital’s GitHub repository.

Buildroot, a tool for easily generating complete Linux system images for embedded platforms through cross-compilation, has announced official support for the open RISC-V instruction set architecture following the merging of a patch set by Embecosm’s Mark Corbin.

Merged into the Buildroot source this weekend, as confirmed on the project’s Twitter account, Mark’s patch set is part of Embecosm’s larger support for the RISC-V architecture which has included work on a RISC-V-compatible tool chain and experimenting with support for vector extensions in the GNU Compiler Collection (GCC) and LLVM.

Detailed in full on the Embecosm blog, which includes full instructions for configuring Buildroot for RISC-V support and evaluating it using the open-source QEMU emulator, Mark’s patches add support for the 64-bit variant of the RISC-V instruction set architecture. The toolchain has already proven suitable for building a Linux 4.15 kernel suitable for booting on QEMU.

More detail on Mark’s patch set is available from the Buildroot mailing list, while those looking to get started will find full instructions on the Embecosm blog.

The growing support for free and open-source silicon (FOSSi) isn’t welcomed by all, however: Cambridge-based processor giant Arm has telegraphed increasing concern regarding the threat from free and open source silicon (FOSSi) cores, offering engineers access to free-as-in-beer Cortex-M intellectual property (IP) in an attempt to keep them within its own ecosystem.

That interest in free and open source silicon (FOSSi) has been growing is no secret: Companies like Western Digital and Nvidia have begun shifting away from proprietary cores with royalty-bearing licences to FOSSi cores, many built on the RISC-V ISA, which require no licence payments or royalties and which permit full modification and customisation as required. Arm is only too aware of this: earlier this year the company launched an aggressive marketing campaign specifically targeting RISC-V, though it was quickly pulled following considerable backlash from the community and its own engineers.

Now, Arm is having another go at convincing developers to stick on its own ecosystem, offering embedded-focused Arm Cortex-M cores with no licence payments or royalty fees required – but its efforts are very much free-as-in-beer rather than free-as-in-speech.

As part of the company’s DesignStart programme it has announced that developers are able to download Arm Cortex-M1 – a variant of its Cortex-M0 core tailored for use with field programmable gate arrays (FPGAs) – and Arm Cortex-M3 cores with no payment required, providing they are for use with Xilinx FPGAs. The offer does come with strings, however: a mandatory licence agreement which contains various covenants against reverse-engineering, use outside product development and shipping, and – interestingly – preventing the use of the cores for comparative benchmarking, suggesting the company may be concerned with how its IP holds up against the latest and greatest FOSSi equivalents when running on the same FPGAs.

Those interested in applying for Arm’s free cores can find links on the official website, with the Cortex-M1 available now and the Cortex-M3 due to arrive in November.

Project maintainer Wilson Snyder formally announced Verilator 4.0 at the ORConf open silicon event this weekend, following a month’s beta-testing of the popular Verilog hardware description language (HDL) simulator.

Originally developed in 1994 by a Digital Equipment Corporation (DEC) Core Logic Group team led by Paul Wasson for the conversion of Verilog code to C code during the development of the Alpha processor, the source code for Verilator was released by the company in 1998. In 2001 Wilson Snyder became the project’s maintainer, working with contributors to rewrite the tool in C++ for a considerable performance boost – and for a tool which was already outperforming the competition.

Announced during ORConf 2018 this weekend during a presentation by Wilson, Verilator 4.0 brings a range of improvements over previous releases: multithreaded model generation, better optimisations for large blocks, still-further improved performance, support for runtime arguments, new reloop optimisation for repetitive assignment compression, and a range of bug-fixes. It does come with the note, however, that as a major release any patches developed with the 3.9 branch in mind and which have not yet been applied upstream may require considerable rework to apply to Verilator 4.0.

More information on the new release is available from the Veripool website, alongside installation instructions.

Sysmocom’s Harald Welte has announced a steep discount on his company’s stock of Fernvale kits, development boards put together by Andrew ‘bunnie’ Huang and Sean ‘Xobs’ Cross for cellular networking projects, dropping the price per kit from €110 to €58.82 (excluding VAT.)

Unveiled during a presentation at the 31c3 event in 2014, Fernvale is an open hardware and software platform based on a reverse-engineering of the low-cost Mediatek MT6260 system-on-chip. As well as being a capable embedded computing platform in its own right, Fernvale allows for use of the baseband processor – opening up one of the last barriers to truly open cellular networking development, a feature which attracted Harald to the project and saw sysmocom purchase 50 kits for resale.

“This decision was made purely for the perceived benefit of the community: make an exciting project available for anyone,” Harald explains. “With that kind of complexity and component density, it’s unlikely anyone would ever solder a board themselves. So somebody has to build some and make it available. The mark-up sysmocom put on top of bunnie’s manufacturing cost was super minimal, only covering customs/import/shipping fees to Germany, as well as minimal overhead for packing/picking and accounting.”

With more than half the initial stock of boards still in-hand, though, Harald has decided it’s time for a sale: the price of a Fernvale DVT2 kit, which includes the Frond mainboard, Spore analogue frontend board, Blade keypad and expansion board, a camera-to-JTAG adapter cable, LCD display with touch sensor, and mounting accessories, has been dropped from €110 to €58.82 (excluding VAT.)

While the company warns that the boards are aimed primarily at “embedded hardware and system-level software [reverse] engineers who know what they’re doing” and come with no software or documentation, there are numerous projects out there based on the Fernvale system – including an ongoing effort to port the OsmocomBB baseband stack to the board.

The newly-discounted Fernvale kits are available now from the sysmocom shop, while AB Open’s manufacturing division Ground Electronics also sells a custom-designed acrylic housing.

Satellite communications giant Iridium has announced a partnership with Amazon’s Web Services arm to launch a globe-spanning cloud-powered communications network for the Internet of Things (IoT): Iridium CloudConnect.

Based on Iridium’s constellation of 66 cross-linked communications satellites, Iridium CloudConnect ties the company’s satellites into the Amazon Web Services (AWS) cloud computing platform – meaning that it’s possible to build AWS-powered IoT services with live communication anywhere on the globe, the company claims, including the 80 percent of the planet not currently served by traditional cellular connectivity.

“Iridium CloudConnect will completely change the speed at which a satellite IoT solution can be deployed and will allow existing AWS customers to keep everything the same on the back end, while opening up the opportunity to quickly expand their coverage,” claims Iridium chief executive Matt Desch of his company’s new product. “This is a major disruption for satellite IoT. Costs will drop, time to market will speed up, risk will be reduced, and AWS IoT customers that choose Iridium CloudConnect can now enjoy true global connectivity for their solutions.”

CloudConnect is based on Iridium’s existing IoT communications platform, which boasts around 630,000 active devices at present. The new global version will go live some time in 2019, the company has promised, with more information available on the company’s IoT microsite.

Finally, Dangerous Prototypes’ DirtyPCBs, a popular service for low-cost production of printed circuit boards, is expanding its custom cable offering and making it a dedicated website – called, unsurprisingly, DirtyCables.

Originally based on a simple script designed to consolidate internal PCB orders for submission to low-cost manufacturers in China, DirtyPCBs quickly became one of the most popular services for PCB production among low-volume and cost-sensitive customers building prototypes. Since launching with an exclusive focus on printed circuits, the site has been slowly branching out into stencil production, SLA 3D printing, bill of materials (BOM) fulfilment, and custom cable design and production.

It’s the latter that is now the focus of a major upgrade, receiving a new user interface and its own dedicated website. “This is a from-scratch rewrite of the editor at DirtyPCBs with new features based on your requests,” explains Dangerous Prototypes’ Ian Lesnet. “[Including] isometric connector drawings with pin numbers save a trip to the datasheet; improved connector selector with room for additional info; one to many ‘Y’ connections; same connector ‘U’ connections; bigger, cleaner interface.”

The new editor is available in preview mode on the dedicated website, but at present can’t be used for cable orders; those looking to actual buy a custom cable are advised to use the old editor on DirtyPCBs.