Project maintainer Wilson Snyder formally announced Verilator 4.0 at the ORConf open silicon event this weekend, following a month’s beta-testing of the popular Verilog hardware description language (HDL) simulator.

Originally developed in 1994 by a Digital Equipment Corporation (DEC) Core Logic Group team led by Paul Wasson for the conversion of Verilog code to C code during the development of the Alpha processor, the source code for Verilator was released by the company in 1998. In 2001 Wilson Snyder became the project’s maintainer, working with contributors to rewrite the tool in C++ for a considerable performance boost – and for a tool which was already outperforming the competition.

Announced during ORConf 2018 this weekend during a presentation by Wilson, Verilator 4.0 brings a range of improvements over previous releases: multithreaded model generation, better optimisations for large blocks, still-further improved performance, support for runtime arguments, new reloop optimisation for repetitive assignment compression, and a range of bug-fixes. It does come with the note, however, that as a major release any patches developed with the 3.9 branch in mind and which have not yet been applied upstream may require considerable rework to apply to Verilator 4.0.

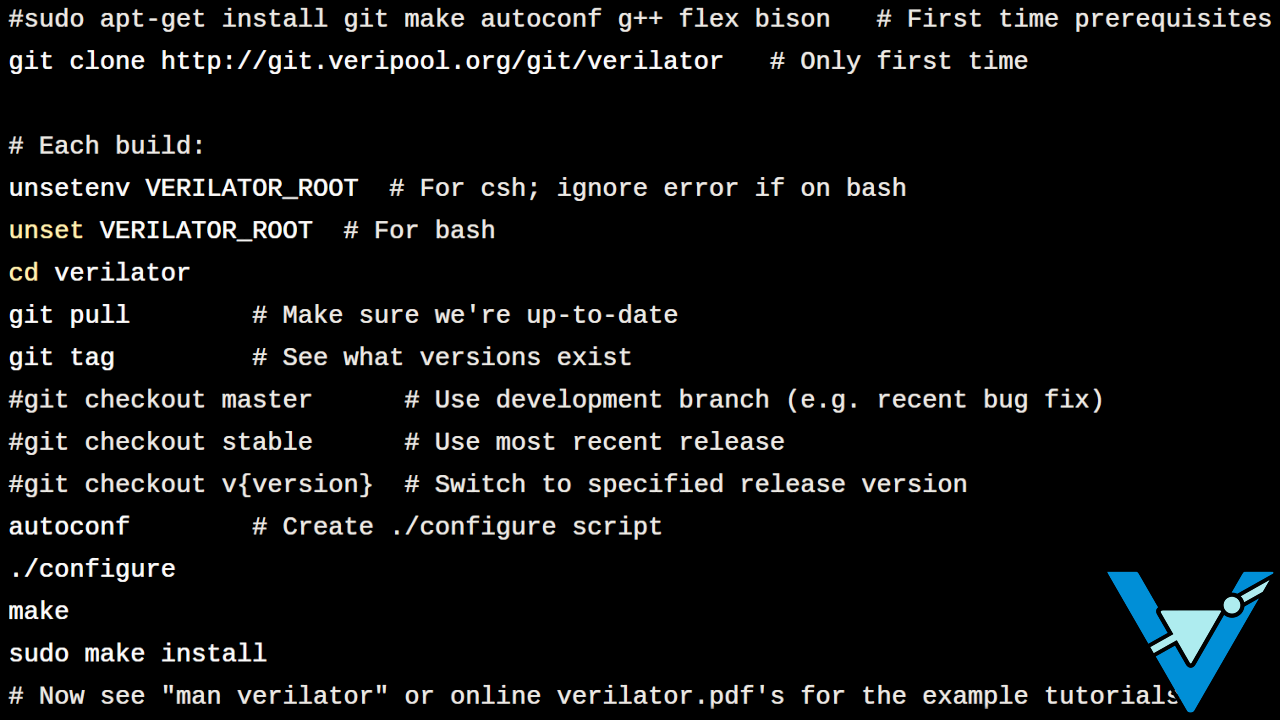

More information on the new release is available from the Veripool website, alongside installation instructions.