When working with brand-new silicon designs, particularly free and open source silicon, there’s a bit of a bootstrapping issue: you want to write software for the new silicon, but there’s no silicon yet available; nobody wants to go to the expense of making the silicon, meanwhile, when there’s no software to use it.

The answer is a three-pronged approach: emulation, soft-core implementations running on a field-programmable gate array (FPGA), and finally application-specific integrated circuits (ASICs) – the latter of which are, for the first time, becoming accessible as far down as the hobbyist level thanks to initiatives like OnChip’s Itsy-Chipsy.

For the burgeoning RISC-V ecosystem, things start – as they always do – at the emulation level. Using tools like Qemu, the open-source emulation engine, developers can simulate a RISC-V processor core and accessories on a CISC x86 desktop or laptop. There’s a trade-off, of course: the emulation is frequently slow, and it can sometimes be difficult to determine whether an issue encountered should be blamed on the silicon core being emulated or the emulator itself.

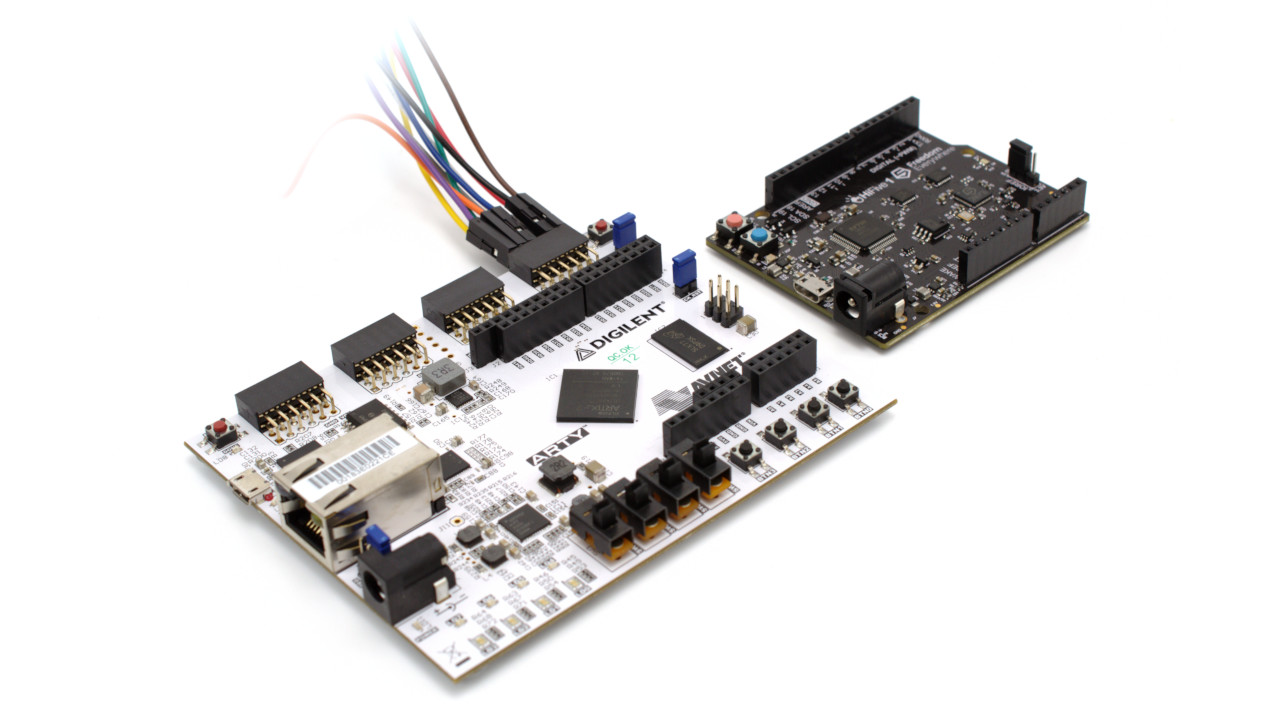

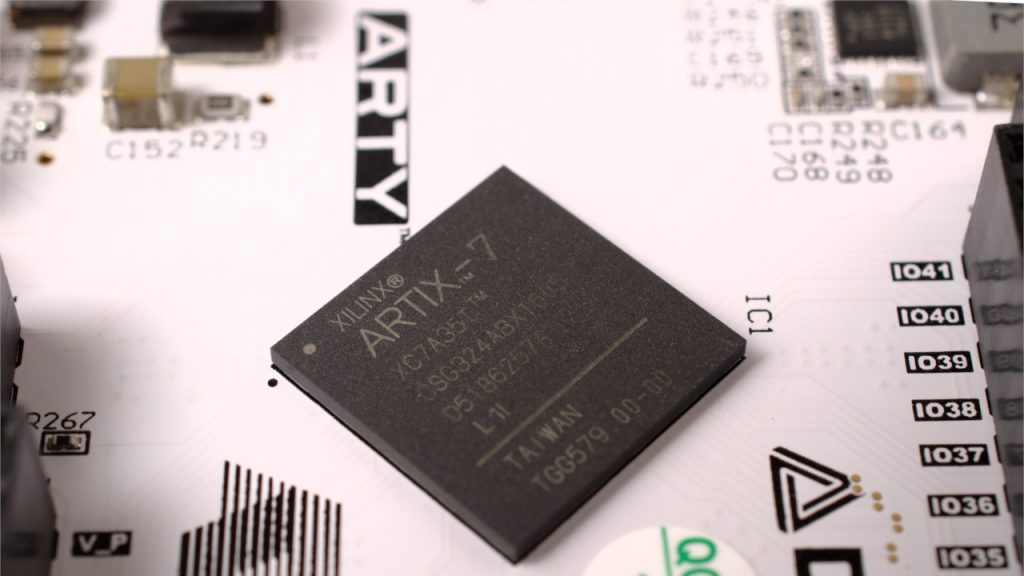

The next step is an FPGA running a RISC-V core. For our experiments with RISC-V, this comes courtesy of a Digilent Arty development board running SiFive’s Freedom E300 core IP. Because the core is now running in hardware, things zip along a lot faster – and if there’s a glitch, there’s no emulation layer to work through during debugging.

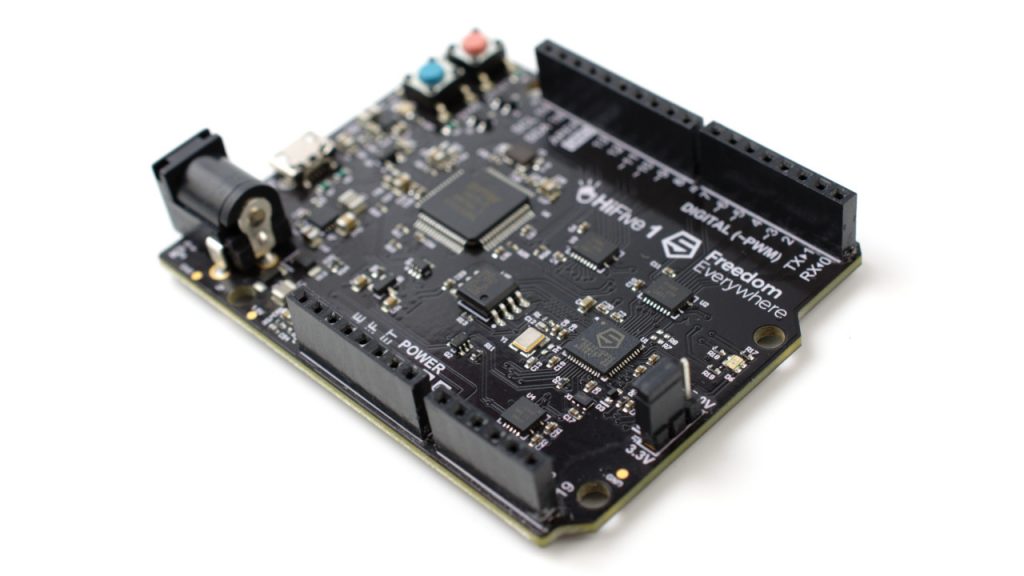

FPGA boards like the Arty aren’t perfect, though. The Freedom E300 core running on the Arty’s FPGA is limited to a clock speed of 65MHz and draws considerably more power than you might expect. This comes into sharp focus when comparing it to the SiFive HiFive1, an ASIC implementation of the same Freedom E300 core IP: the default clock speed of the HiFive1 is 320MHz, a significant improvement on the same core running on the Arty’s FPGA, while drawing around half the power during active computation.

Even where ASICs are available, as in SiFive’s range of RISC-V cores, there’s another consideration: flexibility. The RISC-V ecosystem is one of the most rapidly-changing in the semiconductor industry, and while an FPGA can be quickly flashed with a new release of a core design an ASIC is fixed in perpetuity – at least until someone pays for another tape-out and production run.

In terms of which is better, it really depends on what you’re trying to do: for initial experimentation and ultra-low-cost development, emulation can’t be beaten; an FPGA allows for improved performance and, potentially, reliability but with a higher up-front cost; an ASIC, either purchased off-the-shelf from companies like SiFive or created in-house via services like Itsy-Chipsy, offers peak performance and the lowest possible power draw, but ties you in to the silicon’s current state-of-the-art.