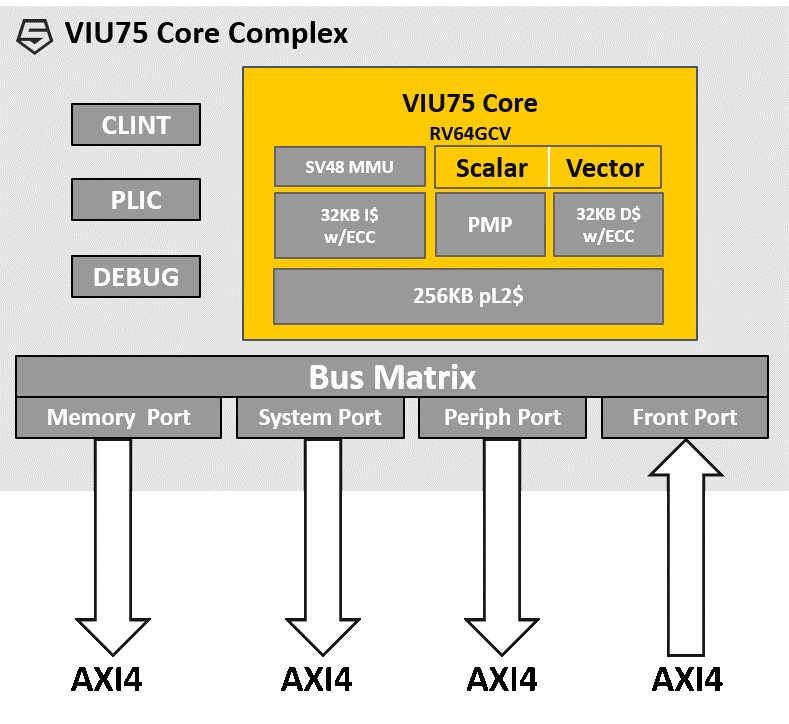

At the Linley Fall Conference 2020, SiFive Chief Architect and co-founder Krste Asanovic announced the RISC-V based VIU7 series. In that, the VIU75 CPU core is 64-bit, runs Linux, and supports “RV vector extension”.

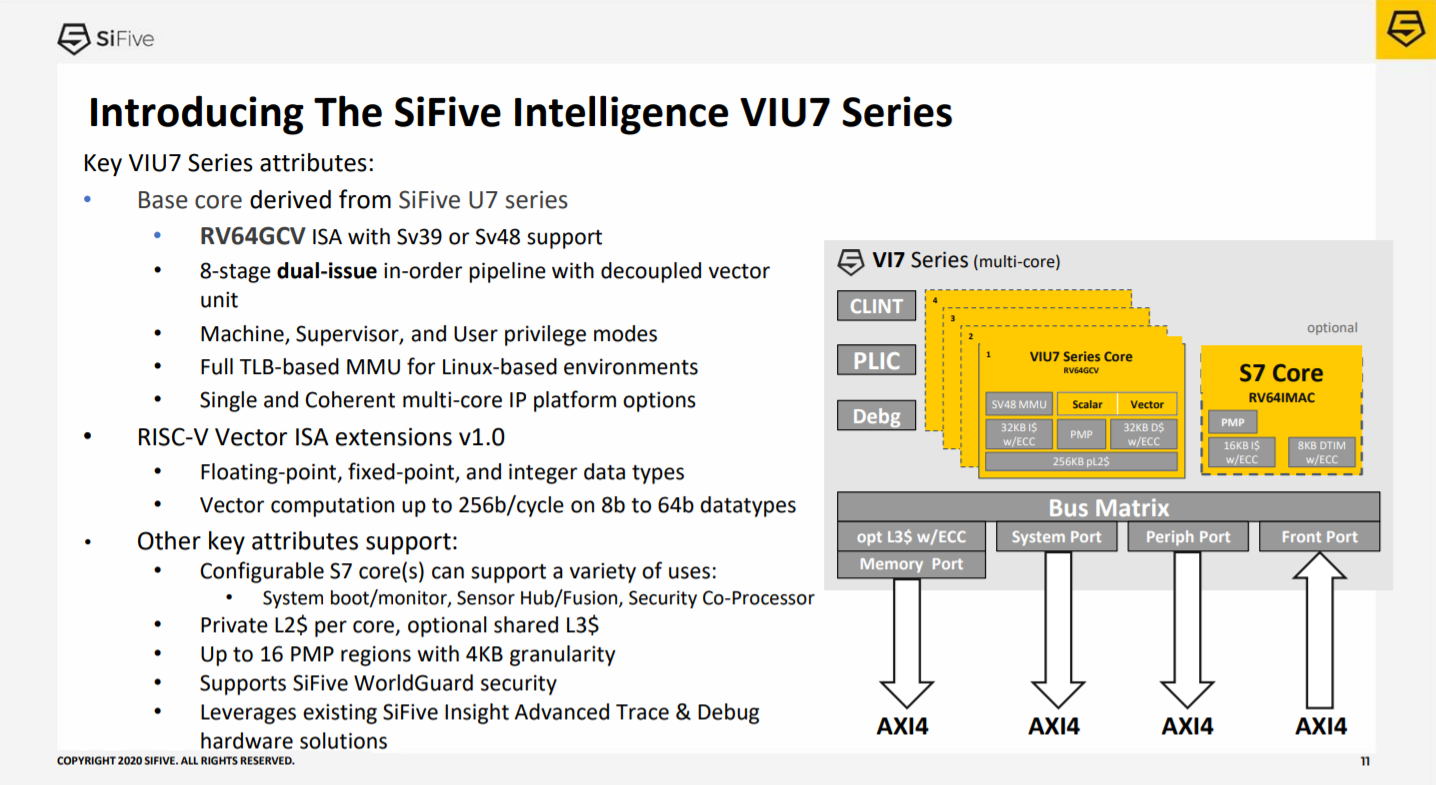

When it comes to RISC-V based core IP, SiFive has always dominated with new CPU IP with a huge portfolio. The RISC-V core VIU75 comes from the VI7 series and U cores. The VI7 series has a high-performance, 8-stage dual-issue in-order pipeline with an integrated vector unit, while the U core family are 64-bit application processors (Linux, data center and network baseband). The CPU IP cores in the VIU7 series are VIU75 and VIU75-MC.

Let’s first take a look at the VIU7 series. The base core of the SiFive U7 series is RV64GCV ISA with sv39 and sv48 support. There is an 8-stage dual-issue in-order pipeline with a decoupled vector unit.

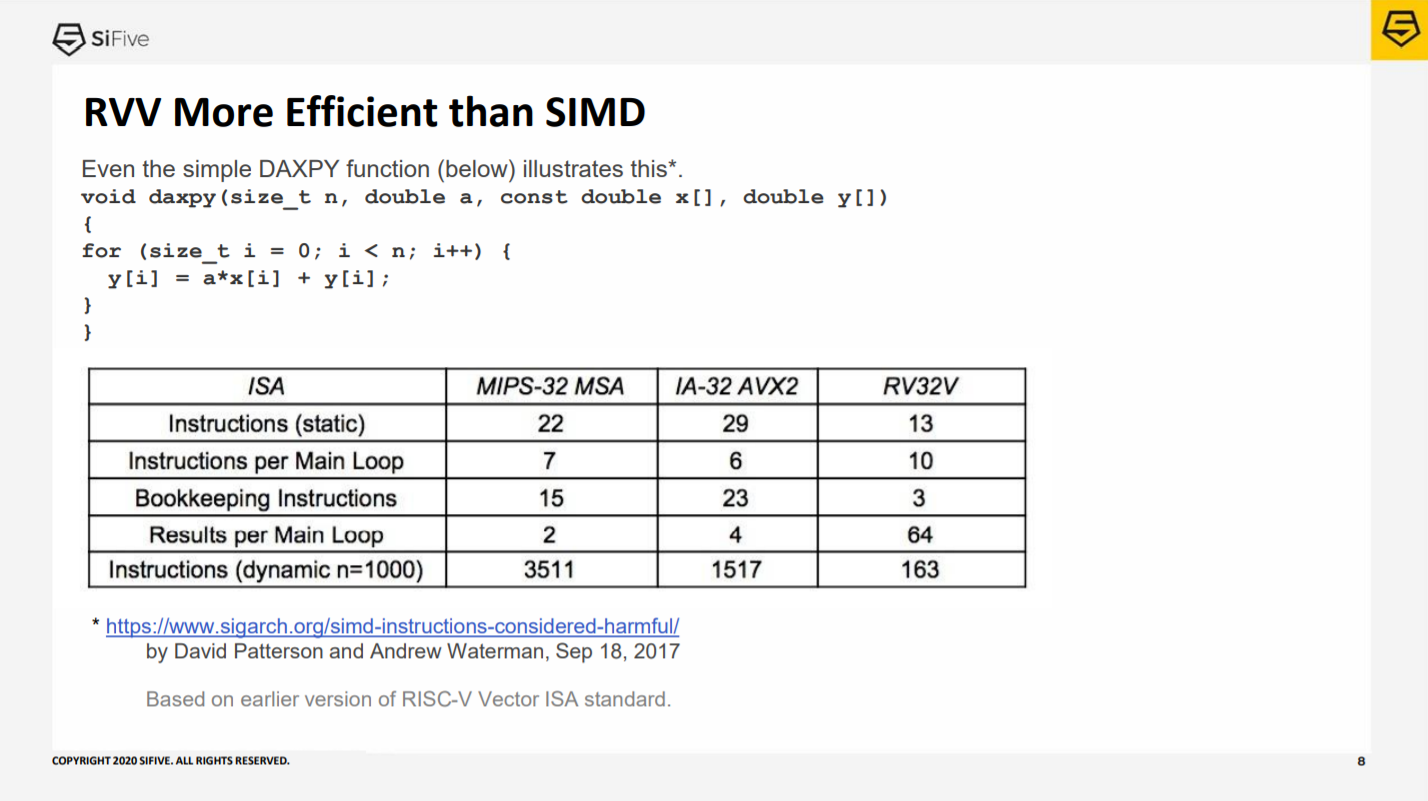

The RISC-V V Vector (RVV) ISA extension is one of the most important highlights of this series of CPU IP cores. Even though the current specs “RISC-V “V” Vector Extension Version 0.9” (draft status), SiFive is confident the core will support version 1.0. The challenge with the SIMD instruction set architecture is with vector length specific (VLS) to pick the right vector register size. RISC-V has solved this problem by designing a variable length vector instruction set.

For 64-bit RISC-V, vector processors typically execute two, four, or eight 64-bit elements per clock cycle. A vector processor with N 64-bit elements per register computes on vectors with 2N 32-bit, 4N 16-bit, and 8N 8-bit elements. This figure shows that the RVV is more efficient than SIMD.

The VIU75 core also has a base core derived from the U7 series. It has RISC-V Vector ISA extension with fixed-point, floating-point, and integer data types and vector computation of up to 256bits/cycle on 8 bits and 64 bits data types. It also supports a private L2 cache, also up to 16 PMP regions with 4KB granularity.

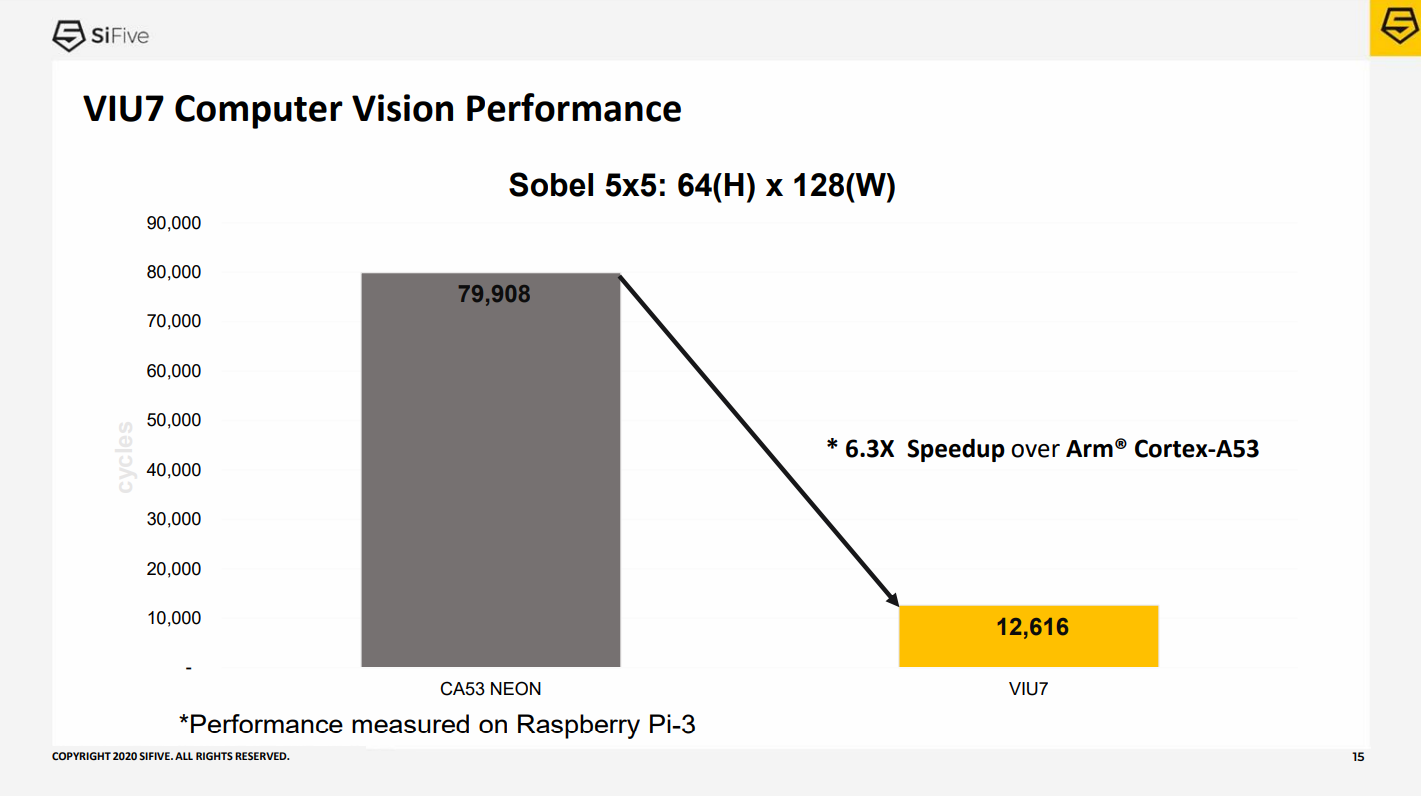

Besides all this, when VIU7 is tested against the ARM Cortex-A53, it showed 6.3 times speedup. The performance is measured on Raspberry Pi-3.

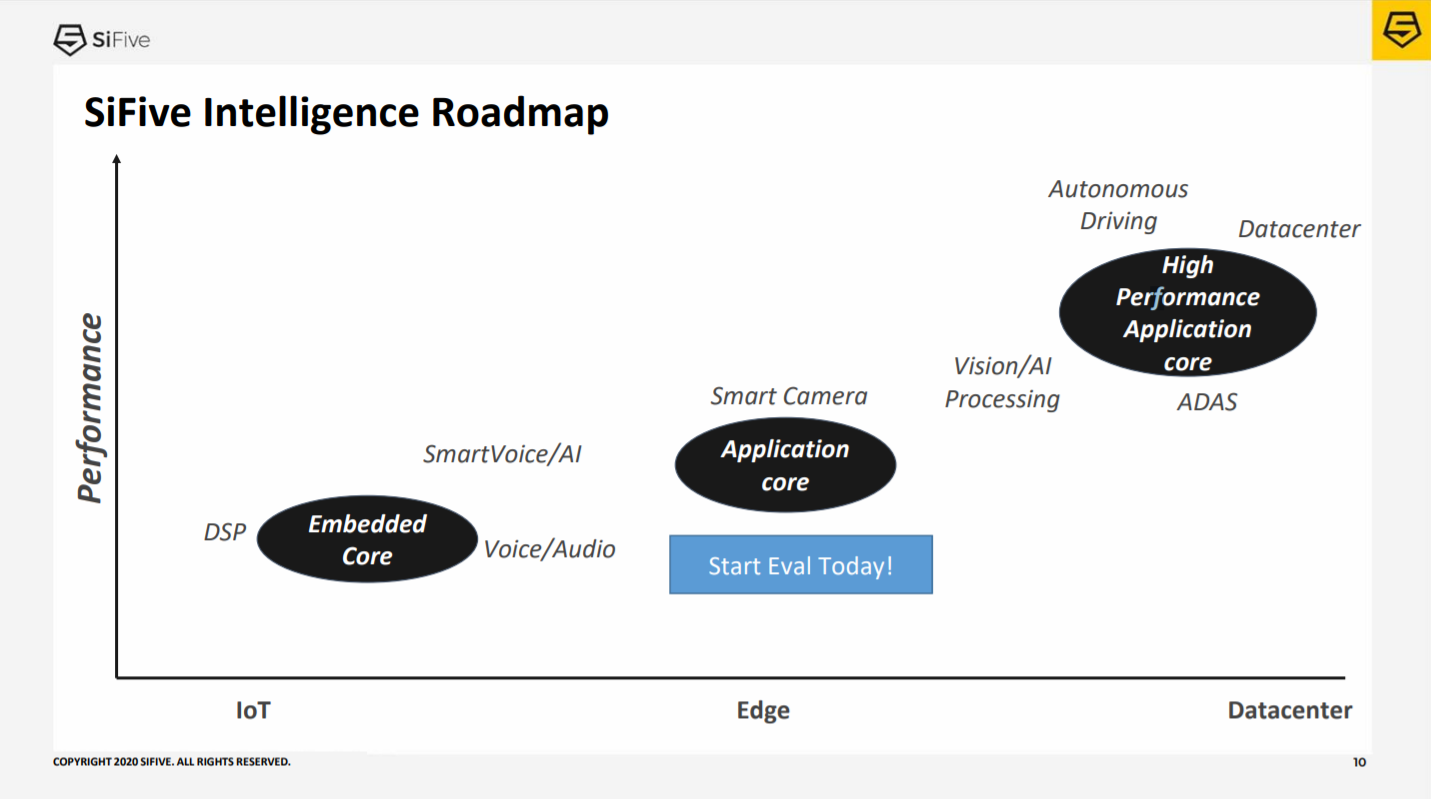

Xilinx VCU118 FPGA supports single and multicore VIU7 cores. The FPGA has 4GB DDR DRAM, SD card, and other peripherals with Linux and embedded runtime environment. It uses SiFive Freedom studio integrated development environment and is used as part of the evaluator system. The targeted applications for VIU7 Series are edge and big data analytics, autonomous machines, edge computing, 5G infrastructure/ base stations, AR/VR/MR/XR, and even smart NICs.

Source: All the images are from SiFive slides at Linley Fall Conference 2020.