Semiconductor Engineering’s Brian Bailey has published a piece on the growth of RISC-V, including comment from industry experts including SiFive’s Krste Asanovic and Microsemi’s Ted Speers – and the conclusion that 2019 will be a year of major design wins for the open instruction set architecture.

Beginning with a look at the troubles besetting those clinging to Moore’s Law – the observation turned mandated development target by Intel co-founder Gordon Moore that the number of transistors on a leading-edge part trends toward a doubling roughly every 18 months – and the silicon industry’s search for alternatives, Brian’s piece delves into the growth of RISC-V and predictions for the future.

“With RISC-V, any innovation that happens in the hardware, by collaboration, will create an economic benefit that will be massive,” Microsemi’s Ted Speers, one of the industry experts quoted in the piece, explains. “But who gets rewarded, or how the rewards get funnelled, still has to be figured out.”

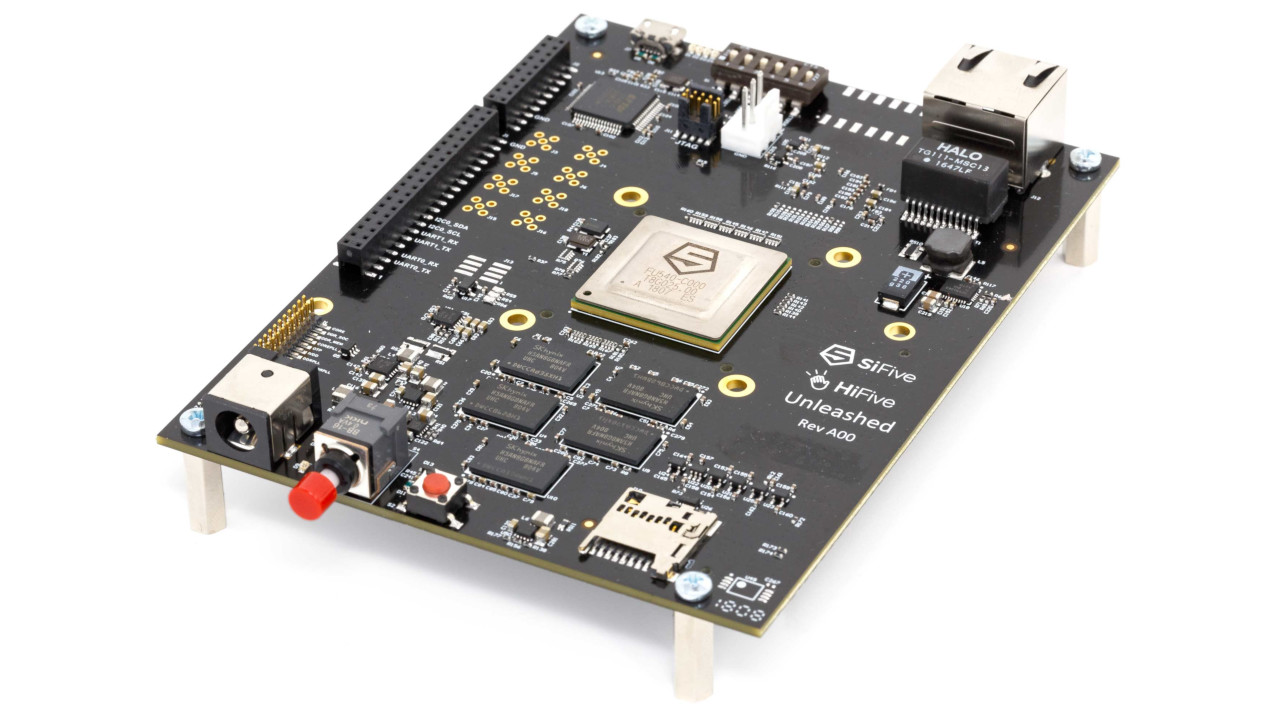

“The old model was that you choose a vendor of the core and you get their ISA,” adds SiFive co-founder and RISC-V Foundation chair Krste Asanovic, on the flexibility RISC-V and other free and open source silicon (FOSSi) initiatives bring. “The new model is, ‘I choose RISC-V and then I choose the vendor. I can use a different vendor for every chip, for each product. I can build my own cores. I can use an open source core or a commercial supported core from one of a number of vendors.'”

While Brian’s piece highlights some of the issues the FOSSi movement will have to navigate in the coming years, it ends on an extremely positive note: “2019 will be the year where you will see a lot of high-profile RISC-V design wins,” predicts Codasip’s Chris Jones, “in application areas previously dominated by legacy architectures.”