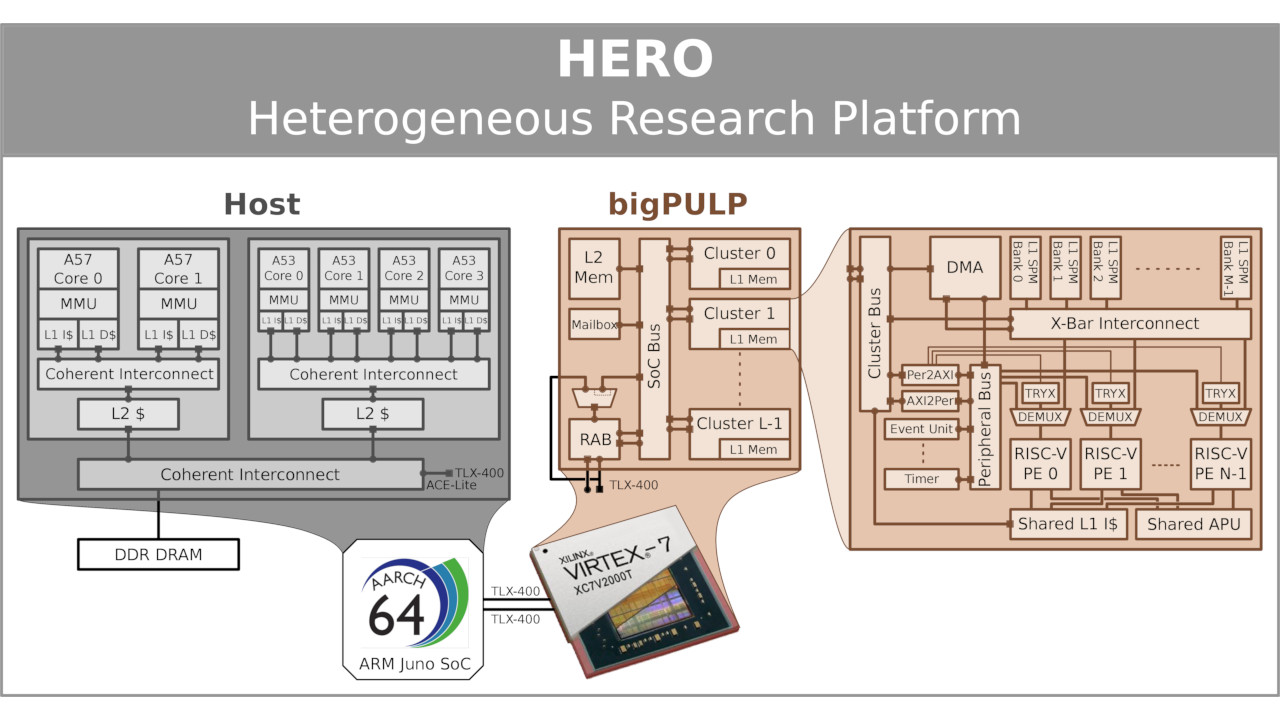

The Parallel Ultra-Low Power (PULP) Platform team has announced the release of its latest creation: HERO, the open heterogeneous research platform combining an FPGA-based RISC-V many-core accelerator with an Arm Cortex-A host processor.

“HERO combines a PULP-based open-source parallel many-core accelerator implemented on FPGA with a hard ARM Cortex-A multicore host processor running full-stack Linux,” its creators explain. “HERO is the first heterogeneous system architecture that mixes a powerful ARM multicore host with a highly parallel and scalable many-core accelerator based on RISC-V cores.

“HERO offers a complete hardware and software platform which advances the state of the art of transparent accelerator programming using the OpenMP v4.5 Accelerator Model. The programmer writes a single application source file for the host and uses OpenMP directives for parallelisation and accelerator offloading. Lower-level details such as differing ISAs as well as shared virtual memory (SVM) between host and accelerator are handled by our heterogeneous toolchain based on GCC 7, runtime libraries, kernel driver and our open-source hardware IPs.”

The platform itself, created in partnership with the Eurolab-4-HPC2 project, is based on a Xilinx Zync ZX706 evaluation kit running an eight-core 32-bit RI5CY-based “Mr. Wolf” PULP cluster with 256KiB of shared L1 scratchpad memory, 4KiB of shared L1 instruction cache, 256KiB of shared L2 scratchpad and instruction memory, and a newly-developed input–output memory management unit (IOMMU) featuring 32 variable-size entry L1 and 1,024 page-size entry transaction lookaside buffers (TLBs).

More information on Hero, which is released under the Apache Licence 2.0, can be found on the official website.