The OpenPiton project has announced a partnership with the PULP Platform to combine the OpenPiton open-source research processor platform with the 64-bit Ariane RISC-V core, creating what is described as “the ideal permissive open-source RISC-V system.”

The Parallel Ultra Low Power (PULP) Platform announced Ariane, a 64-bit application-class RISC-V design, back in February, while the OpenSPARC-based OpenPiton research processor reached Release 7 in June. Now, with Release 10, OpenPiton is joining forces with PULP to create what the pair are calling OpenPiton+Ariane.

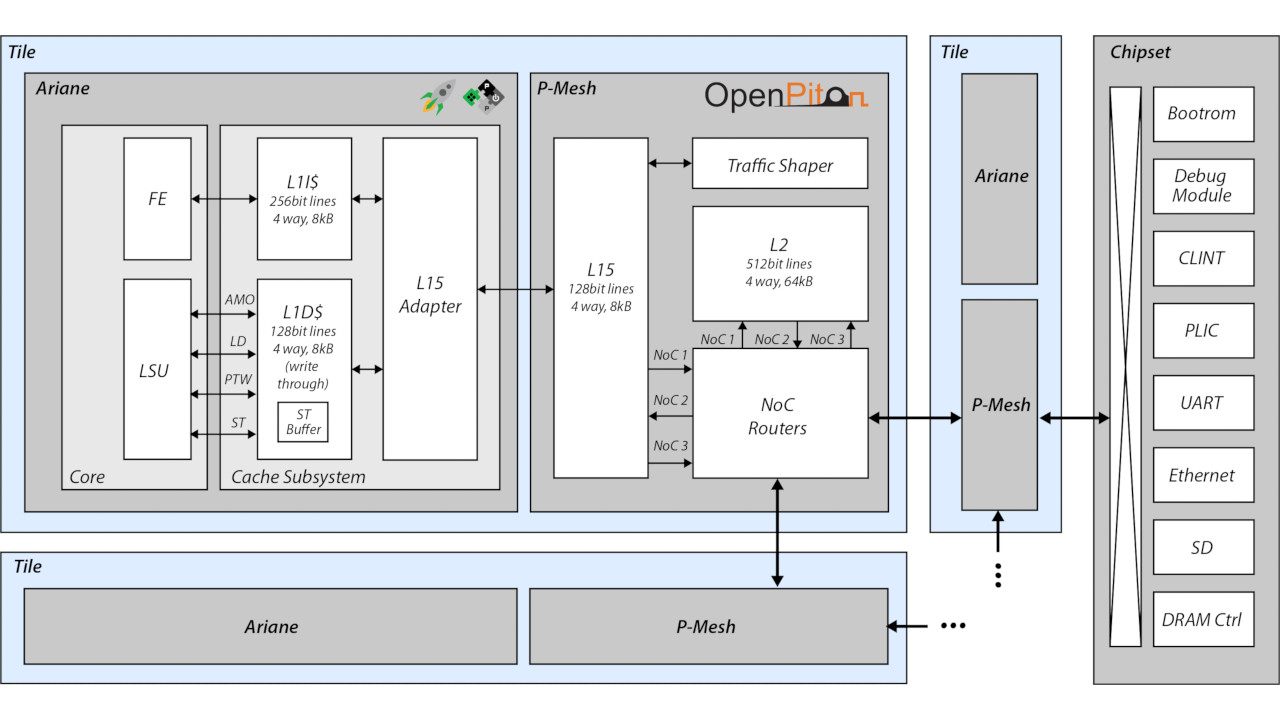

“The Princeton Parallel Group led by David Wentzlaff, and the Digital Circuits and Systems Group of ETH Zürich led by Luca Benini have joined forces to bring you the OpenPiton open-source research processor platform with first-class support for 64-bit Ariane RISC-V cores,” explains OpenPiton’s Jonathan Balkind in the announcement. “The latest update of the open-source Ariane processor, Ariane IV, now supports the P-Mesh cache system from OpenPiton, and with today’s OpenPiton release 10 we have our first working system.

“Going forward, OpenPiton will be the go-to multicore environment for Ariane. Likewise, Ariane will have first-class upstream support in OpenPiton. Together, OpenPiton+Ariane provides the ideal permissive open-source RISC-V system that scales from single-core to many-core.”

Details on simulating the new OpenPiton+Ariane are available on the project’s GitHub repository, while more information on the partnership can be found on the OpenPiton website.