The Parallel Ultra-Low Power (PULP) Project has celebrated its fifth birthday with a retrospective, discussing the progress made since its inception during a meeting at the University of Bologna in May 2013.

“It has been exactly 5 years since Luca Benini started the PULP (Parallel Ultra Low Power) project in a meeting attended by a handful of people squeezed in a tiny office in the University of Bologna,” writes Frank K. Gurkaynak, director of the Microelectronics Design Centre at ETH Zürich, in the retrospective piece published to business networking platform LinkedIn. “We are very proud that our work is finding applications and recognition in the ‘real world,’ and has proven itself to be more than ‘a toy that academics play with.’

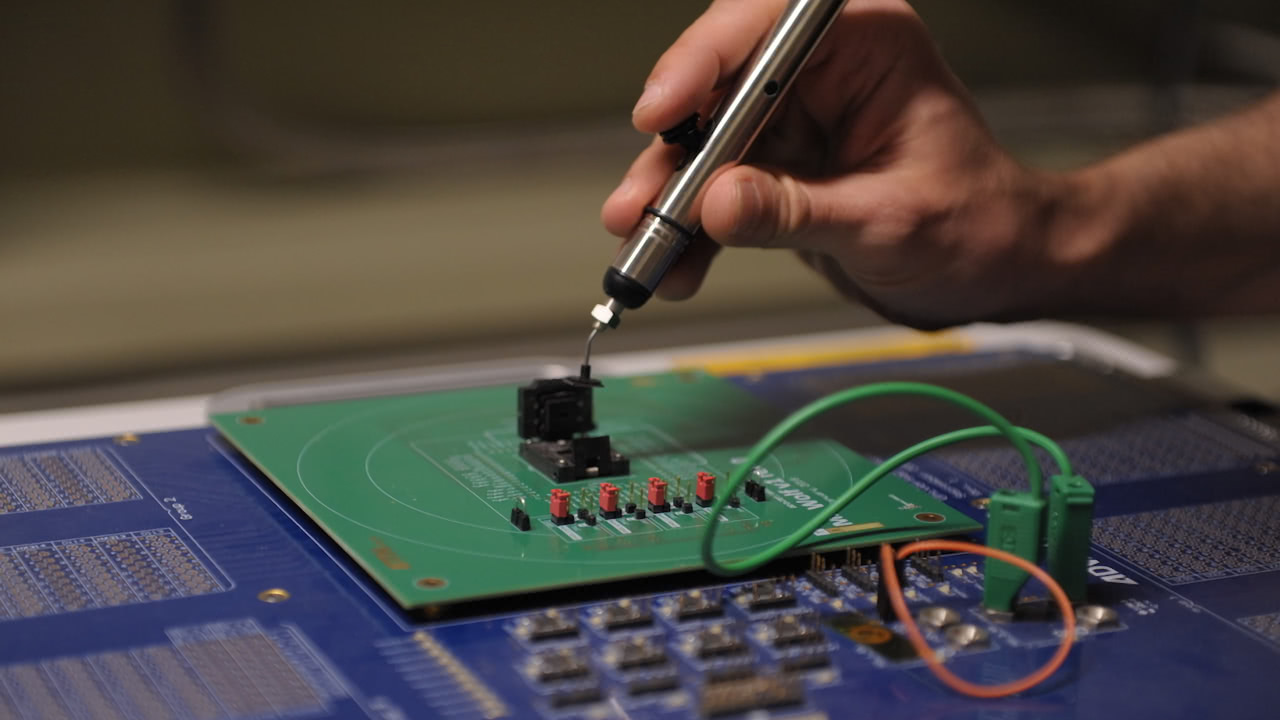

“In the 5 years since we launched the PULP Project, we have developed and tested more than 20 ASICs [Application Specific Integrated Circuits] in various technologies. We are expecting our latest chip, Poseidon, in Globalfoundries 22FDX technology back from manufacturing any moment. The HDL code for the PULP based blocks used in this chip is already available for everyone to use on our GitHub page (just to clarify: at the moment licensing restrictions allow us to provide only HDL code), giving everyone who is interested access to silicon proven IP.

“There are still many skeptics of the open source hardware movement, and I will not be able to convince everyone that open source hardware has a future. However I can tell you that, as the main PULP development team at ETH Zurich and University of Bologna we are committed to continue to support high-quality open source hardware and we are in discussions on participating several exciting projects that we hope to be able to announce soon.”

More information on the PULP Project and its release can be found on the official website.