SiFive’s implementation of the open RISC-V instruction set architecture (ISA) has scored another design win, this time to power a smart reprogrammable storage device aimed at the data centre and enterprise markets from Mobiveil.

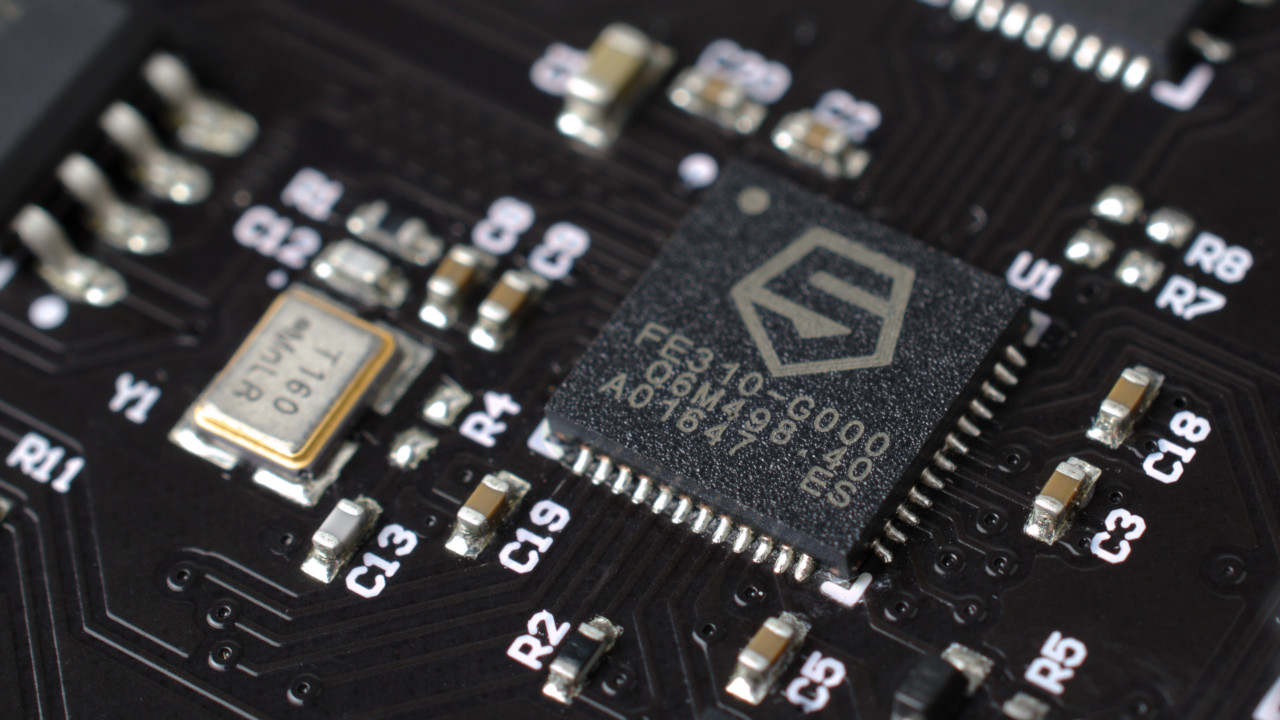

Fresh from the announcement of the world’s first RISC-V based SSD controller and SSD implementation from Fadu, RISC-V pioneer SiFive has confirmed a design win that will see the company’s E51 and U54 multi-core RISC-V intellectual property (IP) used in Mobiveil’s reprogrammable FPGA-based solid-state storage products.

“We chose to partner with SiFive on this SSD platform solution as their cores offer the lowest area and highest power efficiency of any similar cores in the market,” claims Ravi Thummarukudy, Mobiveil’s chief executive, of the partnership. “Mobiveil’s advanced FPGA-based board enables reliable and robust system solutions that can be easily tailored by enterprise and data centre designers. Having a RISC-V CPU in an FPGA, designers can optimise their solution to target [the] latest flash devices from multiple suppliers. Furthermore, the FPGA-based board solution enables enterprise and data center designers the flexibility to re-architect how storage is deployed in their high-performance cloud.”

“RISC-V is the ideal processor for data centre storage applications,” adds Shafy Eltoukhy, senior vice president of operations at SiFive Inc. “The cores’ highly efficient microarchitecture and configurability provide the optimal performance needed to execute the latest storage programs data centres are employing to accelerate access to the exploding amounts of information being compiled today. Working together with Mobiveil to make this RISC-V based SSD platform enables customers to accelerate their RISC-V based product development efforts.”

Western Digital has previously confirmed it is working on RISC-V-powered storage processing products of its own, based on core IP licensed from SiFive, with a view to shipping a billion cores a year.