Princeton University’s OpenPiton free and open source silicon (FOSSi) project has announced what is claimed to be the world’s first open-source, general-purpose, heterogeneous-ISA processor: JuxtaPiton.

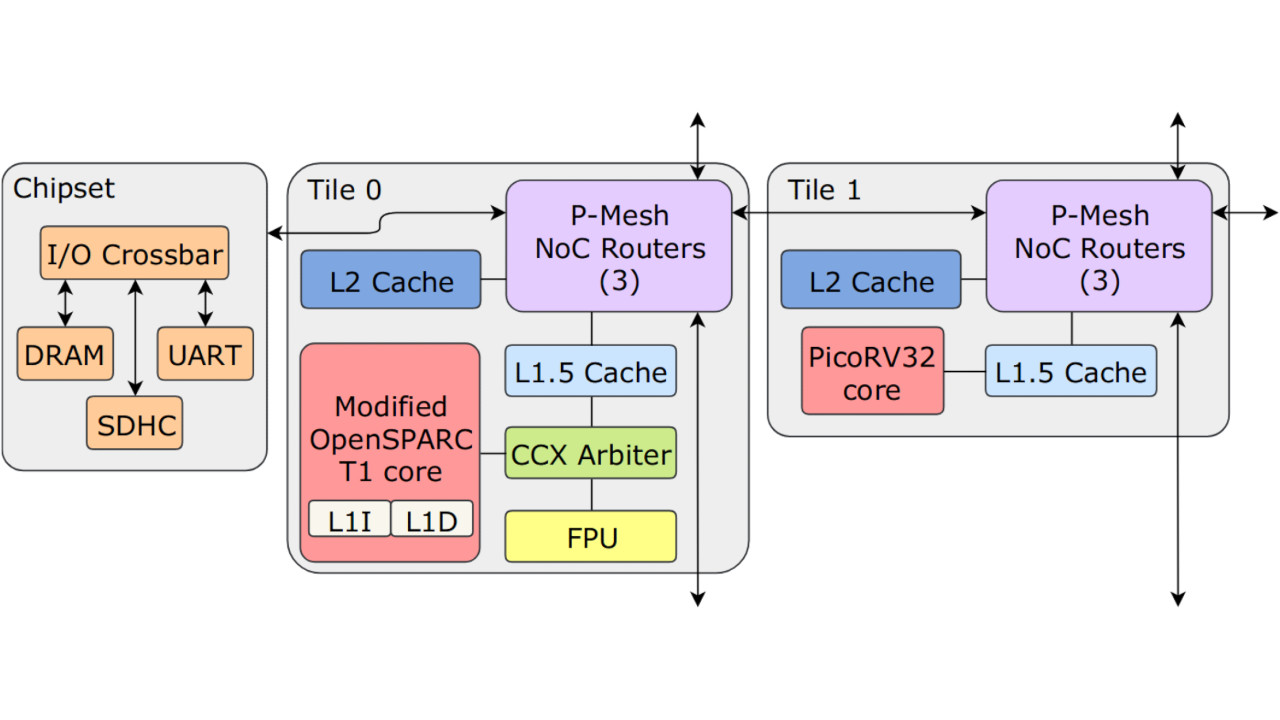

Built by combining the SPARC v9-based OpenPiton with Clifford Wolf’s PicoRV32 RISC-V core, JuxtaPiton is something unique. “JuxtaPiton inherits all of the capabilities of OpenPiton, with the added ability to instantiate chosen tiles with RISC-V cores, rather than the usual OpenSPARC T1 core, which uses the SPARC v9 ISA,” OpenPiton’s Jonathan Balkind explains. “When implemented on FPGA, JuxtaPiton can boot Debian Linux on an OpenSPARC core as with OpenPiton. With the addition of a PicoRV32 core in the system, the OpenSPARC core can offload the execution of RISC-V binaries to be natively executed on the PicoRV32 core. When the RISC-V binary needs to make a system call, it can proxy it on the OpenSPARC core instead.”

The new JuxtaPiton RISC-V capabilities form part of OpenPiton v9, released earlier this week. As with all releases, downloads are available both from the OpenPiton website and the project’s GitHub repository.

The work on JuxtaPiton, which is understood to be the first open-source general-purpose processor design to include heterogeneous instruction set architecture (ISA) capabilities, is to be presented at the FPGA 2019 conference by lead author Katie Lim. Her paper, written with Jonathan Balkind and David Wentzlaff, is available now via arXiv.org uder the title “JuxtaPiton: Enabling Heterogeneous-ISA Research with RISC-V and SPARC FPGA Soft-cores.”