Eidetic Communications’ chief technology officer Stephen Bates has announced initial support for peer-to-peer direct memory access (P2PDMA) on the RISC-V instruction set architecture, showing a 2.8GB/s throughput between controllers.

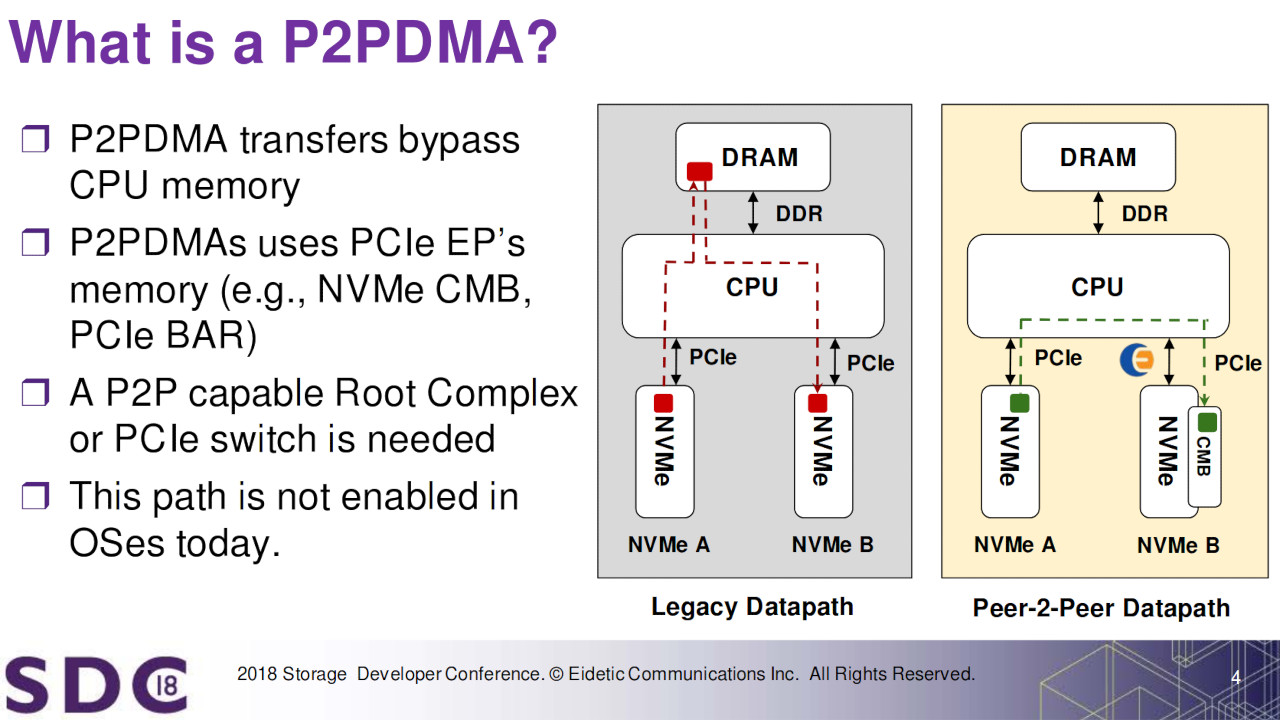

Designed to address the bottleneck between high-speed PCI Express (PCIe) devices and the CPU, P2PDMA allows for data transfer to occur directly between PCIe devices without using CPU-controlled memory. As a result, it offers considerable performance benefits: a presentation from Eideticom during the 2018 Storage Developer Conference (PDF warning) showcases a 50-fold improvement over standard Non-Volatile Memory Express (NVMe) offload drivers.

Now, that benefit is also available for RISC-V users. “We ported the P2PDMA patches for Linux to the RISCV64 ARCH and confirmed P2PDMAs work in both QEMU and on real hardware provided by SiFive and Microsemi Corporation and Intel Corporation and Eideticom,” explains Eideticom chief technology officer Stephen Bates via LinkedIn, showing off “~2.8GB/s of P2PDMA for one NVM Express CMB to a NVMe namespace on another controller (both below a PCIe switch).”

Stephen has indicated that additional results will be published at December’s RISC-V Foundation Summit in San Jose, while the patches have been made available via his GitHub repository.