Today, while the term “free and open source silicon” might not be heard around every water cooler, it’s certainly becoming more common. Projects like RISC-V, which aim to create instruction set architectures which can be used in processors from ultra-low-power microcontrollers all the way up to many-core high-performance computing products, have become big news – and big business – thanks to the fact that anyone is free to use, hack, create, experiment, and release products on them without paying a single penny in licensing or royalties.

The free and open source silicon (typically shortened to “FOSSi”) movement didn’t begin with RISC-V, however. It has a history stretching back considerably further than that, even as far as the early days of personal computing.

The Early Years

With traditional silicon development usually taking place in a very closed, secretive environment, the first semi-open and truly-open silicon parts caused quite a stir. Perhaps the most famous, though firmly in the semi-open category, is is the Berkeley RISC Project, whose publicly-accessible research papers would inspire Cambridge-based Acorn engineer Sophie Wilson to develop what was at the time known as the Acorn RISC Machine architecture and which found subsequent success under Arm Holdings as the central ISA for the overwhelming majority of the world’s smartphones, tablets, and other embedded devices.

The output of the Berkeley RISC Project itself would later be commercialised as Sun Microsystems’ SPARC architecture. “The SPARC Instruction Set Architecture (ISA) has been open since inception,” explains Shrenik Mehta, who led the OpenSPARC team at Sun Microsystems – the company’s biggest free and open source silicon effort. “It could be freely downloaded from SPARC International.”

Sun Shines on the Way Forward

Developed in 2005 and publicly released in 2006, OpenSPARC wasn’t the first ‘open’ release from Sun: microSPARC IIep, a 32-bit SPARC implementation, had its source code released in 1999 under the company’s Community Source Licence, previously used for a Verilog implementation of the specialised picoJava microprocessor, which permits free use but not modification and demands a three percent royalty on volume production.

“Almost every year, Sun released a new processor product and management would ask if the product could also be released under open source,” Mehta explains. “Transition to multi-core created the opportunity. We converted the engineering discussion into a business discussion with the level of investment required. I would consider it a top down decision.

“Sun always wanted to expand the ecosystem around SPARC architecture. We were looking for opportunities which would create a pull from the market vs. a push from Sun to create the market. Transitioning from the single core to multi-core created the opportunity. It would be disruptive and Sun would be able to get enough PR (vs. spending marketing dollars.)

“Before the final go-ahead to execute on the project, the team had to complete risk assessment on patent infringement, discovery of bugs by the community, and impact to shipping silicon product, and the download experience – most common at that time was music download and immediate replay of music. If someone waited to download the entire package, what would they do? We created separate packages for hardware design, performance, firmware, to ensure in 30 minutes or less they can compile the design. The team also had to decide on the open source licence – GPL, BSD, etc.”

To Boldly Go

Sun wasn’t the first to market with a FOSSi offering, however. Both the company’s OpenSPARC and the earlier release of the microSPARC IIep project were beaten to market by the GPL/LGPL licensed 32-bit SPARC-V8-based LEON core developed by the European Space Research and Technology Centre (ESTEC) in 1997 with a VHDL model publicly released by ESA’s Jiri Gaisler in October 1999. The two weren’t direct competitors, though: “The LEON SPARC architecture is a 32-bit architecture optimised for space applications,” Mehta explains. “OpenSPARC is based on a 64-bit, multi-core implementation. LEON designs were written in VHDL; the OpenSPARC designs are all in Verilog. Two different products with different target markets.”

The release of LEON proved the vanguard of what became a horde of FOSSi projects. OpenRISC launched in 2000 under the same GPL/LGPL copyleft licence and offering a MIPS-like architecture initially in 32-bit form with a later 64-bit variant. OpenRISC proved beyond a doubt the commercial desirability of open silicon solutions in a range of markets: Samsung famously used the OpenRISC 1000 core in a range of its digital TV products where previously it would have relied on a proprietary alternative, while the TechEdSat-1 cubesat, deployed to the International Space Station (ISS) in October 2012, featured a custom Linux computer built around the OpenRISC architecture.

These notable successes were soon joined by a plethora of other cores, some little more than educational toys and others fully-fledged attempts to usurp the proprietary silicon vendors. The time had come to organise.

The Community Comes Together…

The OpenCores community can trace its origins back to co-founder Damjan Lampret’s work in 1999, initially as a means of reducing duplicated effort and improving collaboration in the open silicon ecosystem. It was on OpenCores that Lampret would release OpenRISC, while the site also played host to a wide variety of other projects: Amber, Zet, Aspida, ZPU, and even specialised designs like the Java Optimised Processor.

The work didn’t go unnoticed by the commercial world. “Shortly after OpenCores/OpenRISC was released Flextronics saw an opportunity to build upon this work ,” recalls Free and Open Source Silicon Foundation director Olof Kindgren.

“Flextronics didn’t contribute any IP per se,” adds Rudi Usselmann, an early member of the OpenCores team. “They hired a small team to develop IPs useful for a SoC around the OpenRISC. If memory serves right, they only hired four of us: Damjan [Lampret], Igor [Mohor], Richard [Herveille], and myself. I can’t remember if there were others.

“They even flew the four of us to Israel, to discuss with management what they wanted. The idea was to give us free reign as long as we where producing useful IP cores. After the initial ‘stunt,’ they funded Damjan to setup a design centre in Serbia. That design centre actually taped out the OpenRISC SoC. Only Damajan and Igor from the original team were part of that centre. Cadence also sponsored OpenCores, by giving out NC-Verilog licences to individuals.”

Initially supported by advertising and sponsorship deals, OpenCores was acquired by Swedish design company OrSoC in 2007 after Flextronics, according to contemporaneous accounts, “lost interest,” and saw rapid growth: from around 20,000 subscribers in 2008 to 95,000 in 2010 and 150,000 in July 2012, the site appeared to be prospering.

“There’s a community called OpenCores that collaborate on chip design and that have developed their own Linux-capable RISC processor,” AB Open’s Andrew Back explained in a 2013 interview with Dennis Publishing’s Custom PC Magazine. “This is mainly used with programmable logic although they are raising funds to get their own silicon made, and the design has even found its way into a custom chip used in digital televisions.”

…And Splits Apart

OrSoC, however, soon adjusted its sights, and in 2015 signed a partnership with KNCMiner to develop machines for Bitcoin mining – a deal which coupled with a divisive attempt to raise cash through a crowdfunded processor core would see it lose focus on OpenCores and lead to a number of the original OpenRISC development team upping sticks and forming the Free and Open Source Silicon Foundation (FOSSi), just in time to see KNCMiner declare bankruptcy a year later. OpenCores itself would be acquired by Dutch startup Oliscience in 2017, and remains under its ownership to this day.

As well as the Foundation itself, which launched in 2015, those pioneers of the open silicon industry who left OpenCores would set up LibreCores as an alternative for hosting and collaboration in open silicon projects.

The collaboration isn’t just digital, either: what was once known as the OpenRISC Conference has become ORConf, an open source digital design conference which attracts a global audience each year – and from semiconductor industry giants like Western Digital, which has sponsored the event, as well as academic research establishments – along with more general open hardware events like those organised by the Open Source Hardware User Group (OSHUG).

The Survivors and Successors

The open silicon ecosystem got its biggest shake-up in 2010, when the University of California at Berkeley – birthplace of the Berkeley RISC Project – unveiled RISC-V, which rapidly clawed its way to the top of the open silicon pyramid. Today, RISC-V boasts backers and implementers as broad as Western Digital and Nvidia to the Indian Institute of Technology Madras (IIT Madras) Shakti Processor Project – which recently succeeded in booting Linux on the first application-specific integrated circuit (ASIC) to be designed and manufactured entirely in India.

RISC-V hasn’t closed out rivals in the open silicon ecosystem, though, and while many of the smaller projects from the early years have fallen by the wayside there are a number still going in original or modified form.

The venerable OpenRISC is still under active development, and inspired the creation of the Open Tiled Manycore System-on-Chip (OpTiMSoc) research project. OpenSPARC, too, remains a going concern thanks to spin-off project OpenPiton, though Oracle itself – which acquired Sun Microsystems in 2009 – has not released a new OpenSPARC design since 2008’s OpenSPARC T2.

The Expansion of the Open Silicon Domain

Processors, however, are only part of the story. A processor core on its own is of little use to anyone, and while the efforts of those in the open silicon ecosystem to developer processor cores are – quite rightly – lauded, a truly open system requires a range of technologies alongside processor IP.

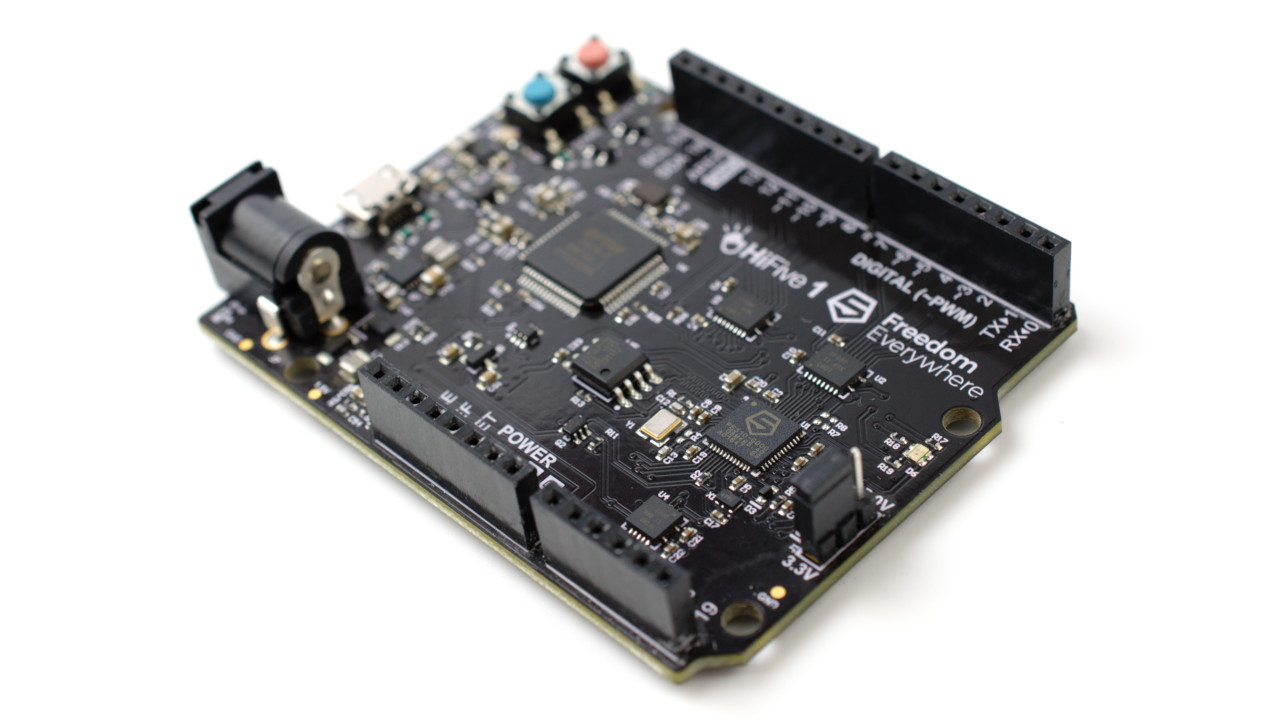

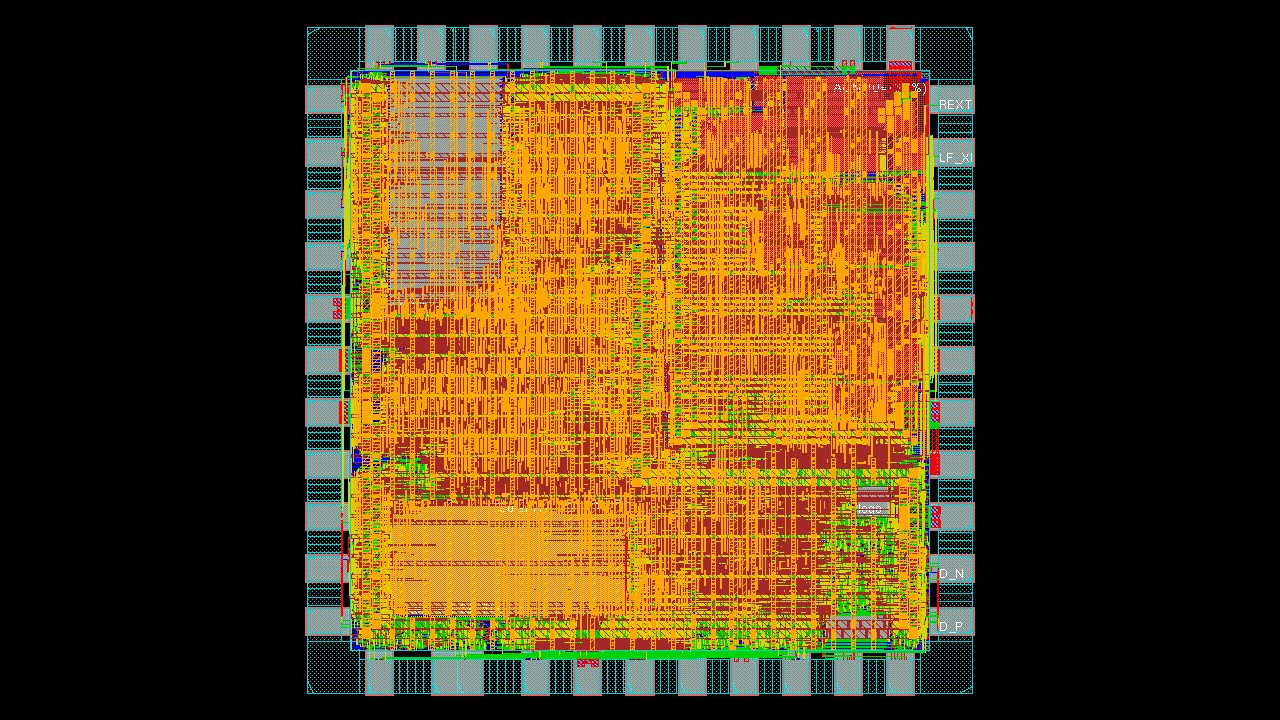

Although open processor cores capture the headlines, there has been plenty of work – both historical and ongoing – into supporting technologies, including some which have found their way into shipping products. A project on OpenCores to develop open inter-integrated circuit (I²C) IP, for example, forms part of RISC-V specialist SiFive’s FU540 processor design as featured on its HiFive Unleashed development board.

A search of the LibreCores database reveals projects for SPI and UART controllers, networks-on-chips (NOCs), open interconnect architectures, DRAM, PCI Express (PCIe), and Ethernet cores, bootloaders, real-time clocks, and even audio controllers, all of which can be used in the creation of a platform which is truly open from the bottom up.

These, in turn, are supported by an open toolchain of software tools allowing a suitably motivated individual to build an open system from open IP adhering to open standards on their open operating system using only open-source software – and, as demonstrated by David Shah at a recent event, even to port this software to the resulting platform and repeat the process.

The Modern Ecosystem

Today, thanks in no small part to the explosion of interest that followed the release of the RISC-V instruction set architecture, the open silicon ecosystem is healthier than ever.

RISC-V itself has spawned a wide array of implementations, both open and proprietary, including lowRISC, PULP Platform, Western Digital’s SweRV Core, and a range of popular products from SiFive.

On the software side, those working with open IP are supported by tools including the Yosys Open Synthesis Suite, Icarus Verilog, FuseSoC, SymbiFlow, MyHDL, and mainstream support for open ISAs in Linux and other kernels.

The community, meanwhile, grows apace: the formation of the FOSSi Foundation and LibreCores community in 2015 has been followed by a number of other announced and impending community launches including the Linux Foundation’s own CHIPS Alliance. Events, from the small to the large, fill the calendar, and it’s no hyperbole to say there’s never been a better time to get involved in open silicon – whether at the hardware or software end of the spectrum.

Work Still To Do

That’s not to say that there isn’t a lot of hard work still to come, of course. Much of the focus for existing open silicon efforts has been in the digital domain, but there’s a need for equivalent projects in the analogue domain too: everything from phase-linked loops (PLLs) to power supply and management IP.

Colombia-based OnChip UIS is currently leading the way in this field, announcing a range of designs which include open analogue IP – along with a debug module, something all too easily overlooked when designing a device.

At the other end of the spectrum is high-speed physical layer (PHY) IP, in particular for fast memory like the double data rate (DDR) family and fast communications like 10-gigabit-Ethernet. “These,” Andrew Back explains, “represent tons of development effort,” but without them open silicon will be required to rely on proprietary IP.

None of these, however, are insurmountable, and just as the early work of the Berkeley RISC Project – and other contemporaneous research projects – effectively spawned the modern open silicon ecosystem, it’s clear that development is by no means slowing down.