Developer Marcelo Samsoniuk has demonstrated just how flexible the open RISC-V instruction set architecture is by creating his own implementation – in, he claims, just one night.

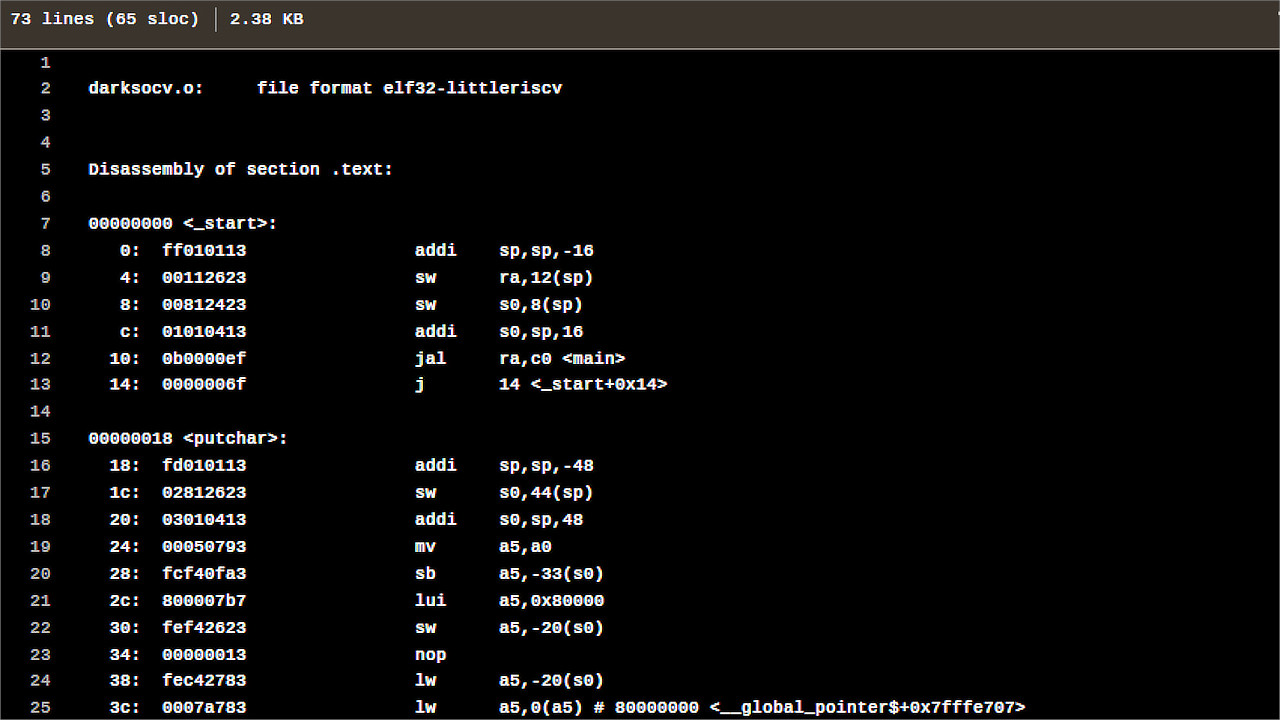

“Developed in a magic night of 19 Aug, 2018 between 2am and 8am, the darkriscv is a very experimental implementation of the open source RISC-V instruction set,” Marcelo writes of his creation. “Nowadays, after one week of exciting sleepless nights of work (which explains the lots of typos you will found ahead), the darkriscv reached a very good quality result, in a way that the “hello world” compiled by the standard riscv-elf-gcc is working fine!

“At the moment, the darksocv [darkriscv-based system-on-chip (SoC) design] is not so relevant and the only function is provide support for the cache controller as well some basic glue-logic,” Marcelo continues. “The proposal in the future is make possible connect the darkriscv to large external memories, as well make possible connect multiple darkriscv cores in a SMP configuration and maybe provide Ethernet communication. Another possible update for the future is integrate the cache controller in the core, in a way is possible a better flow control.”

The full darkriscv implementation can be found on Marcelo’s GitHub repository, under the BSD 3-clause licence.