Opal Kelly has launched a crowdfunding campaign to produce a field-programmable gate array (FPGA) development board, Brain-1, featuring its Syzygy open standard for high-performance peripheral connectivity.

Designed to coexist with existing interconnection standards including PMOD and FMC, Syzygy is claimed to be entirely vendor-agnostic and compatible with products from all major FPGA manufacturers including Xilinx, Intel, Lattice, and Microsemi. While owned by Opal Kelly, which was founded in 2004, Syzygy is licensed freely to vendors creating either carrier systems or peripherals – meaning anyone is free to implement it at any time.

For those just looking to get started Opal Kelly is launching the Brain-1, a development board featuring a Syzygy implementation, along with a range of compatible add-on modules. Described as “the first realisation of a carrier board supporting Syzygy,” the standard Brain-1 includes a Xilinx Zynq 7012S 55,000-cell FPGA and single-core 667MHz ARM Cortex-A9 processor, 1GB of DDR3 memory, a gigabit Ethernet connection, three standard Syzygy ports with 28 input/output (IO) channels and two clock pairs each, and a single Syzygy transceiver port with 18 I/O channels, two each FTP receive and transmit pairs supporting up to 3.75Gb/s data throughput, and a single transceiver reference clock pair.

More information on the board, which is to be released alongside the peripheral boards under an as-yet unspecified permissive licence, can be found on the crowd funding page, while the official website has details on the Syzygy standard.

The RISC-V architecture has received support for Rust, a language that enables development of highly concurrent and highly safe systems.

The Rust language has a syntax that is similar to C/C++ and is targeted at the development of systems that are both highly concurrent and safe, finding use in everything from a microkernel O/S and a cryptocurrency to a container runtime and the latest release of the Firefox web browser.

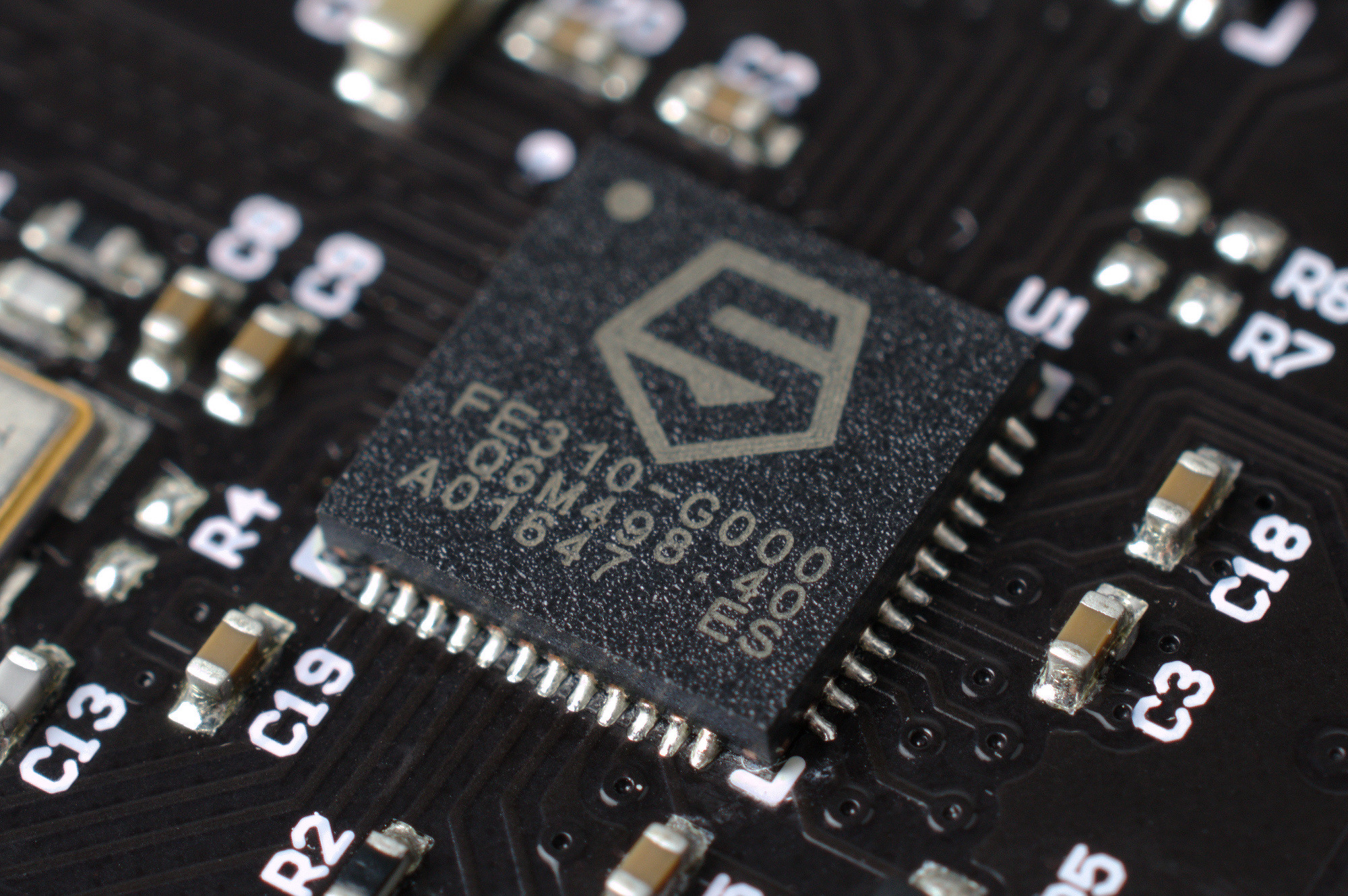

The RISC-V Rust toolchain was first published to GitHub a little over a week ago and comes courtesy of David Craven, who was able to build his port using the RISC-V LLVM tree developed by the lowRISC Foundation. David has also published ‘crates’ — Rust libraries — which provide a BSP for the HiFive1 board plus support for its peripherals.

Analogue and mixed-signal specialist Semtech has announced a “disposable nano-tag” featuring LoRa wireless communication, aimed at remote communication of specific trigger events in everything from healthcare to asset tracking.

“By offering a lower cost, disposable LoRa-enabled tag, we can expand the current landscape of use cases for Semtech’s LoRa devices and wireless radio frequency technology and allow companies to integrate the technology to drive many more diverse IoT use cases,” claims Semtech’s Marc Pegulu. “We believe the number of use cases should expand rapidly as our connectivity and Cloud partners start to leverage the disruptive nature of the LoRa-enabled tag. We continue to introduce leading edge solutions based on Semtech’s LoRa Technology to fully leverage the differentiated capabilities and advantages of the technology’s long-range, low-power and low-cost connectivity.”

The LoRa-standard device is based around an ultra-thin printed battery capable of powering the sensing and wireless hardware, and is presently being piloted ahead of commercial launch in 2018 on flexible tape and paper substrates. More information is available on the official website.

The delightfully bonkers Flashing Light Award has issued a call for ingenious and unusual ways of flashing a bulb, tube, or other vessel that contains neon gas.

The inaugural Flashing Light Prize sought novel approaches to flashing an incandescent light bulb — and the entries certainly did not disappoint, with the winner having employed a Wimhurst machine, ignition coil and a tiny 6v bulb excited with 40kV. However, our favourite by a long measure was the entry where a custom ASIC had been fabricated for the task, designed using that well known EDA tool the Inkscape vector illustration software(!)

The stakes — or rather minimum voltage required — have been upped this year and the challenge is now to flash a bulb, tube or other vessel containing neon gas. With a closing date of 1st February, don’t delay and get those entries in. A worthwhile endeavour for the Christmas break, perhaps…

Finally, the seventh RISC-V workshop, hosted at Western Digital’s campus, has completed with an amazing array of announcements – including that Western Digital itself will be launching data processing products based around the open instruction set architecture (ISA) with a view to shipping a billion cores in the next two years.

The lowRISC project has details of all the announcements from day one and day two of the event, including Western Digital’s product plans, Esperanto’s energy-efficient RISC-V cores for high-performance computing, SiFive’s Freedom Unleashed 500 1.5GHz system-on-chip, and the Celerity 511-core accelerator fabric, among other projects.

The sheer volume of information – and shipping products – announced at this year’s workshop demonstrates the growing momentum behind RISC-V, with more breakthroughs expected at the eight workshop next year.