The rise of low-power long-range radio technologies like LoRaWAN has been a boon for the Internet of Things (IoT), but working in radio brings unique challenges – as demonstrated by Embedded.com’s new guide to optimising the performance of embedded radios.

Written by Chris Lamb and Rod Williams, the guide introduces the core concepts of radio work with a view to addressing the difficulties of balancing the two key aspects involved: the performance of the radio versus the amount of power it requires. The three-page guide also addresses issues unique to radio, such as signal loss and noise sources not present with traditional wired sensor networks.

“To maximise range and battery life, almost all aspects of the device must be considered. The size of the device bounds the antenna efficiency, battery volume and PCB area for an optimum RF implementation,” the pair explain in conclusion. “The care with which the RF [radiofrequency] circuits are designed bounds the range and if done poorly, will degrade the battery life. Similarly, care invested in design of the operational states to maximise sleep time and minimise on-air time can increase range and improve battery life.”

The full guide is available now on Embedded.com.

Also of interest to embedded radio types will be the news that analogue and mixed-signal semiconductor specialist Semtech has announced next-generation chips for LoRa radio devices with a claimed 50 percent reduction in power draw, 20 percent boost in range, and 45 percent reduction in component footprint.

Designed for devices using the LoRaWAN long-range low-power wide area network protocol, Semtech’s new SX1226, SX1261, and SX1268 parts — +22dBm and +15dBm transmit power respectively, with the SX1268 offering +22dBm in frequencies suitable for the Chinese market — are claimed to be a considerable improvement over their predecessors. Each draws as little as half the power of earlier models while in receive mode, offers 20 percent increased range, and is a mere 4mm² package size. The chips also include a new simplified user interface for easier development, a spread-frequency system for better performance in signal-dense environments, and are fully compatible with existing LoRaWAN networks as well as legacy devices through frequency-shift keying (FSK).

“LPWAN IoT [Low-Power Wide Area Network Internet of Things] applications are going through a massive transformation, shifting from trials to large deployments in smart cities, buildings, healthcare, logistics, and agriculture,” claims Marc Pegulu, manager of Semtech’s Wireless and Sensing Products Group, of his company’s latest launch. “LoRa Technology enables an infinite amount of IoT use cases as Semtech pushes for the last mile of connectivity and reinforces its position as the defacto platform for LPWAN.”

All three parts are sampling to selected customers now, Semtech has confirmed, with general availability scheduled for later this quarter alongside full development kits. More information is available on the company’s official website.

Those working with computer vision and neural network technologies will be interested in a one-day workshop in London that provides an introduction to deploying deep neural networks with the Intel Movidius Neural Compute Stick.

Open source frameworks such as Caffe and TensorFlow expedite the development of deep learning applications, and with the addition of the Myriad Vision Processing Unit (VPU) technology from Intel it becomes possible to move these to the edge and embed AI technology in low power devices.

The Intel Movidius Neural Compute Stick (NCS) integrates the Myriad VPU into a compact USB 3.0 peripheral for use in prototyping, validating and deploying deep neural network (DNN) inference applications, with support for Ubuntu host development and deployment, plus deployment support for Raspberry Pi.

On 22nd February 2018 Intel, in partnership with the Open Source Hardware User Group and BCS Open Source Specialist Group, will host a one-day workshop in central London which will provide an introduction to deploying applications with the Intel Movidius NCS and open source frameworks. The event is free to attend and NCS hardware will be provided for use during the workshop.

For further details and to register please see the event page.

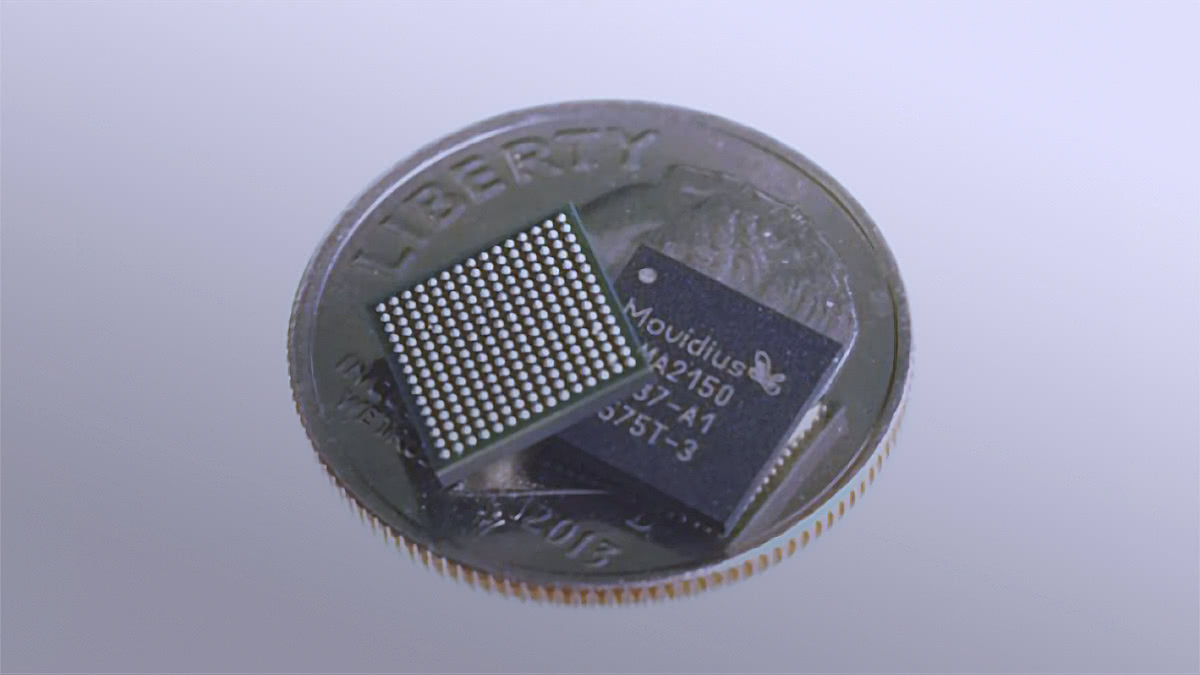

In a fantastic demonstration of its capabilities, meanwhile, Intel’s innovative Myriad 2 VPU has found its way into the drone market through a partnership between start-up Ryze Tech, Intel, and drone specialist DJI.

Designed to offer ease of flight and remote photography with smartphone control, the Ryze Tello is described by the company as a toy – but the technology driving the device is anything but. To simplify its controls, the company has implemented Intel’s Myriad 2 VPU – originally developed by Movidius prior to the company’s acquisition by Intel in 2016 – for hardware-accelerated computer vision that doesn’t drain the 80g micro-drone’s battery.

“The Tello is an impressive drone with so much intelligence packed inside such a small package,” says Remi-El-Ouazzane, vice president and Movidius general manager at Intel’s New Technologies Group. “The incredible vision processing capabilities of the Intel Movidius Myriad 2 enable Ryze to miniaturise the drone and eliminate the need for multiple processors dedicated to each flying function. This is just the beginning of a promising toy market featuring robotics, AI and computer vision technologies.”

Esperanto, a company run by The Case for RISC co-authors Dave Ditzel and Dave Patterson, has announced its first RISC-V products – including a 4,112-core processor aimed at high-performance artificial intelligence (AI) applications.

Detailed in full on WikiChip Fuse, Esperanto’s aim is to produce three intellectual property (IP) core families based on the open RISC-V architecture: ET-Maxion, a high-performance core designed as an alternative to Arm; ET-Minion, a high-efficiency core; and ET-Graphics, the first RISC-V-based graphics processor. Each will be implemented on Taiwan Semiconductor (TSMC)’s 7nm process node, the company has claimed, and will be available in hardware and licensable IP forms.

Esperanto’s first commercial product, though, combines the ET-Maxion and ET-Minion into a monster many-core processor aimed at the high-performance computing (HPC) market, with a view to accelerating deep-learning and other artificial intelligence (AI) workloads. According to details revealed by Dave Ditzel, the part will include 4,096 ET-Minion cores and 16 ET-Maxion cores for a total of 4,112 RISC-V cores on a single chip. The ET-Minion cores will also include extensions for the specific acceleration of machine learning workloads.

No release date has yet been provided, though more information is available on the official website.

Elsewhere in the world of RISC-V Future Electronics has announced the launch of the Avalanche development board, powered by Microsemi’s PolarFire field programmable gate array (FPGA) and shipping with a pre-loaded RISC-V CPU core.

“The Avalanche board is the newest addition to our family of development boards. Avalanche is the lowest cost board available in the market for this innovative PolarFire technology,” claims Future Electronics’ Martin Bernier of the release. “We believe industrial, medical, defense and communication customers will be excited about PolarFire FPGA’s ability to deliver up to 50 percent lower power than other mid-range density devices.”

Featuring 300,000 logic element (LE) FPGA, Wi-Fi, gigabit Ethernet, and various expansion connectors, the Avalanche can be used for general FPGA development or as an entry point into Microsemi’s Mi-V ecosystem for RISC-V development – with Future Electronics pre-loading a RISC-V based CPU core onto the FPGA as standard so it’s ready to use out-of-the box.

The Future Electronics Avalanche board is available in the US now and the UK shortly, priced at £132.98 excluding VAT directly from Future.

Arm’s MBED division has announced the release of LittleFS, a file system designed to offer high-integrity storage for embedded devices with minimal RAM and flash usage.

Built into Mbed OS 5.7 as an alternative to the classic File Allocation Table (FAT) file system, LittleFS is designed to reduce resource usage while adding wear-levelling and power-loss resilience functionality. “LittleFS, the high-integrity embedded file system in Mbed OS is optimised to work with a limited amount of RAM and ROM. It avoids recursion, limits dynamic memory to configurable buffers and at no point stores an entire storage block in RAM,” explains Arm’s Jan Jongboom. “By focusing on a small set of multi-purpose data structures, this high-integrity embedded file system uses 13K less ROM than FAT and 4K less RAM.

“We designed this file system for systems that may have random power failures. It has strong copy-on-write guarantees, and storage on disk is always kept in a valid state. Most storage chips that embedded devices use support a limited set of erases per sector. If you do not have a storage controller with support for wear levelling, the longevity of your embedded device could be compromised. The embedded file system provides dynamic wear levelling to spread data across sectors throughout the full size of the flash. This prevents applications from writing the same sectors too often.”

More details on implementing LittleFS can be found on Jan’s blog post.

Researchers at the University of Manchester have announced graphene-based battery-free sensors which they claim could revolutionise the Internet of Things (IoT).

Using graphene, a layer of carbon one atom thick and which is being hailed as the wonder-material of the future for a range of technologies, in graphene-oxide form, a team of researchers at the University have been able to build wireless humidity sensors which harvest energy from their surroundings with no need for a battery or other energy storage system. While energy-harvesting sensors aren’t new, the team’s use of so-called two-dimensional materials in their construction is claimed to allow for mass production at an extremely low cost – to the point where humidity and other sensors could be added to radio frequency identification (RFID) tags quickly and cheaply.

“This is the first example of printable technology where several 2D materials come together to create a functional device immediately suitable for industrial applications,” claims Professor Sir Kostya Novoselov, project co-ordinator and Nobel Prize recipient for his work in the field of physics, of the breakthrough. “The Internet of Things is a fast growing segment of technology, and I’m sure that 2D materials will play an important role there.”

The team’s work has been published for open access in the journal Scientific Reports.

Finally, our Open Source Digital Design Insights (OSDDI) interview series continues with Professor Elkim Roa, head of the OnChip Group at UIS Columbia.

A modern microntroller or system-on-chip is much more than simply a processor and some digital peripherals, typically integrating a selection of analogue IP also. In this latest episode of Open Source Digital Design Insights we speak with Professor Elkim Roa, head of the OnChip Group at UIS Colombia who are building on the RISC-V architecture and working to address the lack of free and open source silicon (FOSSi) analogue IP, such as LDO, power-on reset, ADC, and DAC, etc.

Previous entries in the OSDDI interview series can be found on the AB Open Vimeo page.