The RISC-V Foundation has announced the launch of a design contest, in partnership with Google, Antmicro, and Microchip, which will see entrants competing to build the smallest and fastest RISC-V soft core implementations on field-programmable gate arrays (FPGAs).

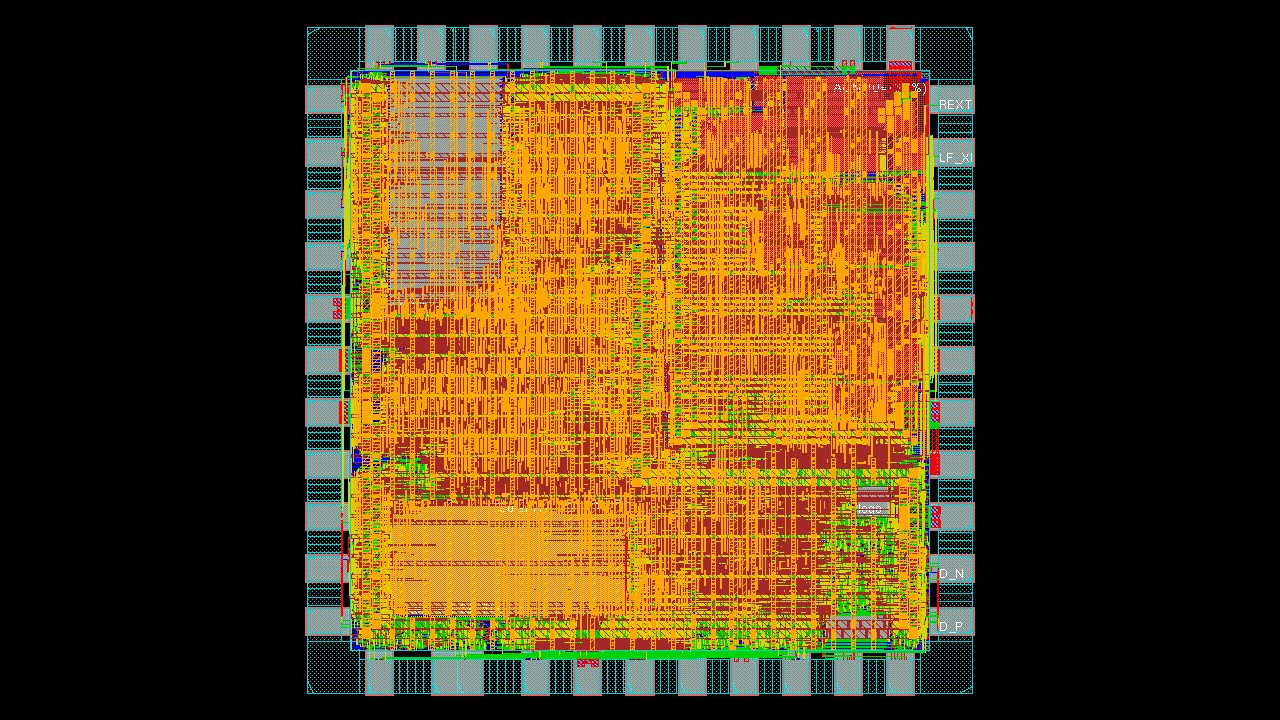

One of the biggest benefits of free and open source silicon (FOSSi) is that you are able to tweak and tailor its design to suit your own needs. To help demonstrate this, the RISC-V Foundation’s design contest is seeking engineers willing to create 32-bit RV32I soft cores and implement them on Microsemi SmartFusion 2, Igloo 2, or Lattice iCE40 UltraPlus FPGA development boards. Each entry will be judged based on two key metrics: size in terms of resource usage, with performance as a tie-breaker; and raw performance in the Dhrystone benchmark.

“As the RISC-V ecosystem has grown, we’ve already seen a wide variety of cutting-edge RISC-V designs in FPGAs as companies and designers take advantage of the free and open model of RISC-V and the flexibility, scalability and extensibility advantages the ISA offers,” explains Rick O’Connor, executive director of the non-profit RISC-V Foundation. “This contest is a great opportunity for designers around the world to experiment with creating ultra-small and high-performance FPGA soft CPU implementations with the RISC-V ISA.”

For engineers on a budget, Microsemi is offering 25 Future Electronics Creative Igloo 2 and 25 Creative SmartFusion 2 FPGA development boards on application, on a first-come first-served basis. The first-prize winner will receive $6,000; second place nets $3,000 plus a Splash Kit and iCE40 UltraPlus MDP development board; third place receives $1,000 plus a PolarFire Evaluation Kit and an iCE40 UltraPlus Breakout Board.

Details of how to enter can be found on the Foundation website, with entries due in by the 26th of November.

Eidetic Communications’ chief technology officer Stephen Bates has announced initial support for peer-to-peer direct memory access (P2PDMA) on the RISC-V instruction set architecture, showing a 2.8GB/s throughput between controllers.

Designed to address the bottleneck between high-speed PCI Express (PCIe) devices and the CPU, P2PDMA allows for data transfer to occur directly between PCIe devices without using CPU-controlled memory. As a result, it offers considerable performance benefits: a presentation from Eideticom during the 2018 Storage Developer Conference (PDF warning) showcases a 50-fold improvement over standard Non-Volatile Memory Express (NVMe) offload drivers.

Now, that benefit is also available for RISC-V users. “We ported the P2PDMA patches for Linux to the RISCV64 ARCH and confirmed P2PDMAs work in both QEMU and on real hardware provided by SiFive and Microsemi Corporation and Intel Corporation and Eideticom,” explains Eideticom chief technology officer Stephen Bates via LinkedIn, showing off “~2.8GB/s of P2PDMA for one NVM Express CMB to a NVMe namespace on another controller (both below a PCIe switch).”

Stephen has indicated that additional results will be published at December’s RISC-V Foundation Summit in San Jose, while the patches have been made available via his GitHub repository.

Developer Clifford Wolf has announced the release of Yosys 0.8, the latest version of the popular open synthesis suite framework, bringing with it a range of new improvements and bug fixes.

Designed to ease register-transfer level (RTL) development, analysis, and formal verification for projects written in the Verilog hardware description language (HDL), Yosys – the Yosys Open Synthesis Suite – was first launched in 2012 as the first full-featured open-source package for Verilog HDL synthesis. Since its initial release, the tool has proven popular among developers looking to ease their synthesis work.

The freshly-released Yosys 0.8 brings with it a number of improvements and bug fixes, including a wide range of new commands, initial support for new circuit development platforms including the CoolRunner-II, eASIC, and ECP5, expanded iCE40, MAX10, and Cyclone IV support, and a number of enhancements to the Verific front-end.

Anyone currently using Yosys is advised to upgrade to Yosys 0.8, which is available to download now from the GitHub repository under the permissive ISC Licence.

Arm’s Mbed division has announced a new operating system to sit alongside its existing Mbed OS: Mbed Linux OS, based on the Linux kernel and tools from the Yocto Project.

“My goal has been to extend the benefits of Mbed OS to IoT products that use Cortex-A silicon,” explains Arm’s Mark Knight, who joined the Mbed team specifically for the project. “We’re delivering this ‘sibling’ OS using the Linux kernel and with tools and recipes from the Yocto Project. This new OS will live alongside Mbed OS and is called the Mbed Linux OS.

“At a time when the price-performance ratio of Cortex-A SoCs continues to increase, it’s possible to deploy ever more advanced processing within IoT devices. This can enable products to handle complex workloads more autonomously, improving availability and placing fewer demands on connectivity to the cloud or edge gateway. Mbed Linux OS is designed for these IoT devices and is deeply integrated with the Pelion IoT Platform to simplify lifecycle management.”

The Mbed Linux OS, mark promises, includes signed secure boot and signed update functionality, the ability to deploy applications in Open Containers Initiative (OCI) complaint containers, optional commercial support with guaranteed service level agreement and platform longevity, support for popular development boards and production-ready modules, and will be available under an open source licence for both the OS itself and its test suites.

The first public version of Mbed Linux OS is due for release in early 2019, the company has confirmed, with interested parties able to register for more information on the official website.

The European Commission has announced a plan to harmonise the radio spectrum allocations for short-range devices in a pair of popular frequency bands, to help support Internet of Things (IoT) project development and deployment.

Adopted as what is known as an “Implementing Decision,” the European Commission’s plan will see additional spectrum made available to short-range IoT deployments operating in the 874-876 MHz and 915-921 MHz frequency bands. “The adopted Decision harmonises technical conditions for spectrum use by short-range devices,” the Commission explains. “It seeks to satisfy the spectrum needs of next-generation RFID devices and innovative ‘networked short-range devices,’ an alternative technological approach to connect IoT devices independently of mobile networks.

“In the context of the adopted Decision, simple examples could be low-cost sensors connected to a network access point to gather soil quality data or sensors and actuators installed in the light posts of a street and connected to a controller to provide smart street lightning. The range of possible applications is manifold and can get much more complex than this. Devices that are more sophisticated can operate in different bands or different portions of a band according to availability and thus can bridge differences in spectrum availability to a certain degree. However, this does not generally hold for short-range devices. Consequently, differences in spectrum access conditions may for instance increase their production costs and create risks of harmful interference with other radio applications and services due to unauthorised use.”

As well as IoT projects, the new spectrum harmonisation will also allow for radio frequency identification (RFID) deployment within the 900 MHz spectrum band allowing for improved reader speed, accuracy, reduced tag size, and better localisation of tagged items. The same decision also brings with it benefits for the railway and military sectors, the Commission has explained.

The full decision can be read on the European Commission website (PDF warning).

Developer Sébastien Caux has released a tool dubbed uConfig which aims to simplify an often-annoying part of the electronic development process: automated conversion between data sheet pin-out diagrams and KiCAD-compatible schematic symbol objects.

Brought to our attention by Hackaday, Sébastien’s uConfig started life as a personal project but has recently been released for public use. The tool takes a PDF-format data sheet in one end, and out of the other comes a KiCAD-compatible library file containing a labelled schematic component for the part.

“The extraction of pin mapping from PDF files is done by parsing datasheet. Poppler is used to extract blocks of text and with magic rules, it sorts the pin numbers and pin labels. Labels and numbers are associated by most relevant pair to create pins. Then, the list of pins is also sorted and associated by packages,” Sébastien explains. “The second part of the tool is named pinruler, to permit a reorganisation following a set of rules named KSS (KiCAD Style Sheet).”

The tool includes both command-line and graphical user interfaces, and has been released under the GNU General Public Licence 3. Full source code is available via the Robotips GitHub repository.

Finally, British artificial intelligence specialist DeepMind Technologies, acquired by Google parent company Alphabet in 2014, has announced the release of a library of building blocks for reinforcement learning in machine intelligence: TRFL.

The TRFL library, pronounced “truffle”, is described by the company as “a collection of key algorithmic components that we have used internally for a large number of our most successful agents such as DQN, DDPG and the Importance Weighted Actor Learner Architecture.” The library includes functions for the implementation of classic reinforcement learning algorithms as well as what the company claims are “more cutting-edge techniques,” both implemented in Google’s open-source TensorFlow language.

“They are not complete algorithms,” the DeepMind team warns, “but implementations of RL-specific mathematical operations needed when building fully-functional RL agents. This is not a one-time release. Since this library is used extensively within DeepMind, we will continue to maintain it as well as add new functionalities over time. We are also eager to receive contributions to the library by the wider RL community.”

The TRFL library is available now from DeepMind’s GitHub repository, under an Apache v2.0 licence.