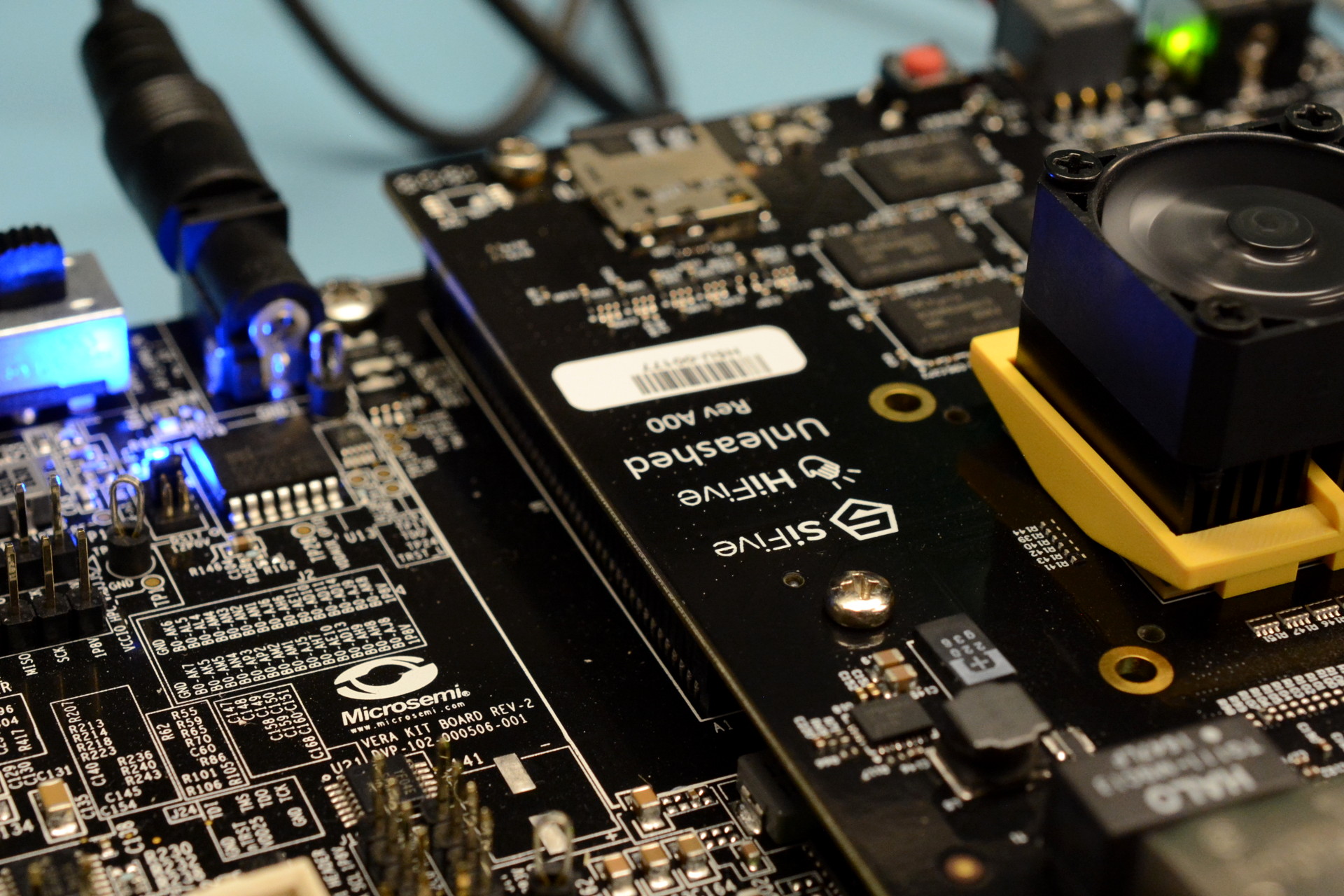

AB Open’s Andrew Back has published a piece on building a personal computer based on the RISC-V instruction set architecture (ISA), using a custom-designed housing containing a SiFive HiFive Unleashed development board and Microsemi Expansion Board.

“While it’s clear that the most significant opportunities for RISC-V will be in democratising custom silicon for accelerating specific tasks and enabling new applications — and it’s already driving a renaissance in novel computer architectures, for e.g. IoT and edge processing — one question that people cannot help but ask is, so when can I have a RISC-V PC? The answer to which is, right now,” Andrew writes of the project.

“The result is a RISC-V powered system that can be used as a desktop computer and thanks to the efforts of Atish Patra at Western Digital, installing Fedora Linux is a breeze. This is obviously not exactly commodity hardware, but it does show that the ingredients are there and the combination provides a powerful development platform for anyone who might want to prototype a RISC-V PC — or indeed a vast array of other applications which stand to benefit from the open ISA.”

The full build is detailed in a blog post and supporting video.

EE Times correspondent Nitin Dahad has pointed to growing troubles for embedded processing giant Arm, and the source should be of no surprise: the growing tide of free and open source silicon (FOSSi) designs, including RISC-V.

That the ability to literally clone a GitHub repository and have a fully-working processor design ready to use or modify with no royalties or restrictive licensing is causing something of a revolution in the semiconductor industry is no secret – RISC-V pioneer Greenwaves launched its entire company and first product for less than the cost of the initial licence payment on an Arm design. That such a concept threatens industry incumbent Arm, too, has not gone unnoticed: the Cambridge-based company, now owned by Japanese technology behemoth SoftBank, launched an ill-advised and since-cancelled aggressive marketing campaign against RISC-V specifically, and recently made some of its Cortex IP available under free-as-in-beer licence agreements.

With even long-time competitor MIPS flying under a FOSSi flag these days, Nitin claims that things are looking tough for Arm – and its customers are responding. “We hear stories about new licensing practices at Arm since it was acquired by Japan’s SoftBank. Arm’s rivals tell us that they are engaged in many more talks with current Arm licensees who are looking for alternatives,” Nitin writes. “Product developers no longer have the luxury of two-year product development cycles. And many don’t have the big budgets for licensing fees, often quoted as the huge barrier to entry for system-on-chip (SoC) design.

“A CEO of a company selling RISC-V IP said that Arm’s days could be numbered. He gives the company no more than five years with its existing business model. The bottom line is that Arm’s approach offers limited flexibility compared to a more open architecture. No one wants to spend months negotiating licence terms under today’s cost and time-to-market pressures.”

Nitin’s full piece, which includes a very IBM-like attitude revealed by one unnamed Arm executive downplaying the very concept of a ‘free’ core, is available on EE Times now.

Internet of Things (IoT)-focused components provider Seeed Studio has begun stocking the Sipeed Tang Primer FPGA development board, a sub-$18 part which features an Anlogic EG4S20 FPGA running a RISC-V soft core.

Designed to offer a full RISC-V implementation in a very small form factor, the Tang is based around the Anlogic EG4S20 field-programmable gate array (FPGA) with 20,000 logic units, around 130KB of SRAM, and 64Mb of SDRAM on a 32-bit bus. The board also includes 8Mb user-accessible flash memory, an I²C controller for a resistive touch screen, TransFlash card socket, sockets for LCD or VGA video output and DVP camera or high-speed analogue to digital (ADC) input, GPIO breakouts, and a micro-USB socket.

The device comes running the E200 Hummingbird RISC-V soft core, a two-stage ultra-low-power implementation designed to compete with the Arm Cortex-M0+ in embedded applications, in the form of a fork dubbed the E203.

According to Seeed, the board’s target applications include high-speed communication interface interconnection projects, machine vision processing at the edge, parallel computing acceleration, and general education surrounding the RISC-V architecture.

Full details are available on the Seeed Studio store page.

Embedded news site CNXSoft has highlighted an upcoming part from Jiangsu Qinheng Co., Ltd, also known as WinChipHead (WCH), which combines a RISC-V core running at 60MHz with Bluetooth Low Energy (BLE) connectivity.

Recently added to WCH’s parts list, the 32-bit microcontroller has been dubbed the CH572 – putting it into the same CH57x family as the company’s Arm Cortex-M0 microcontroller offerings – and is claimed to run at 60MHz. Full details haven’t yet been supplied by the company, but CNXSoft’s analysis of the available information found a part with 10KB of SRAM, 96KB of one-time programmable (OTP) flash memory, Bluetooth Low Energy (BLE) connectivity, USB Host and USB Device support, an 11-channel 12-bit analogue to digital converter (ADC), three 26-bit timers, 11 pulse-width modulated (PWM) pins, two UARTs, one SPI, 23 GPIOs, real-time clock, and watchdog support, all running on a supply voltage of 3.3V or 2.5V and in a QFN28 package.

“CH572 is shown as being ‘在研,'” the site writes, “which I understand means ‘under development,’ so it’s unclear when it will become available. Nevertheless, WCH CH572 is quite interesting, as AFAIK it’s one of the first RISC-V MCUs from a ‘traditional’ silicon vendor that should be fairly easily procurable.”

Thus far, WCH has not detailed exactly which RISC-V implementation – whether off-the-shelf or developed in-house – it is using on the part, nor whether any customisations it has made will be released under a permissive licence or kept proprietary.

More information is available on the CNXSoft website.

A new LoRaWAN sensor platform, dubbed Generic Node, promises to bring low-cost deployment to a wider audience with nine sensors built into a device which is claimed to be available for $25 a unit in medium volume quantities.

The LoRaWAN long-range low-power wide area network protocol is at the heart of a range of community WAN projects around the world, but the growing number of networks need devices on them to prove their true worth. It’s here that the Generic Node aims to fill a gap, offering nine sensors – light, motion, proximity, free-fall, moisture, orientation, water, touch, and temperature – in a weatherproof case running from a single AA battery.

Based on the Arm Mbed OS platform, the Generic Node is designed to be a prototyping platform on which developers can build – complete, its creators claim, with support on modifying the hardware and software and, should it be desired, go-to-market and distribution approaches. Better still, the devices are claimed by Mikael Falkvidd to cost just $25 (around £20) in medium volume quantities.

Full details on the Generic Node, which was shown off in prototype form at The Things Conference late last month, are not yet available, though interested parties are invited to join an early access program on the official website.

EBN editor-in-chief Hailey Lynne McKeefry has penned a piece pointing to the considerable benefits of open hardware, and in particular the RISC-V instruction set architecture (ISA), to the procurement process.

“It’s clear that open source hardware will have a ripple effect, not just on design, but also on procurement practices,” Hailey writes, citing industry experts including RISC-V Foundation executive director Rick O’Connor and Wave Computing’s Art Swift. “With so many organisations exploring the potential of the RISC-V ISA, procurement departments will likely be faced with an explosion of new sourcing alternatives. The list of contenders in the marketplace will range from young startup organization to veteran chip providers such as Marvel, Microchip Technology, NXP, Cadence and others.

“While electronics OEMs won’t necessarily upend their approved supplier lists, it’s likely that new products will appear on many bill of materials (BOM). Further, at least for some organisations, designing and implementing specialised chips is possible, with very little capital or operating expense expenditure required. Other organisations can work with IP development companies to get help in creating the chips they want.

“RISC-V, with its low-cost of entry and designing ease,” Hailey concludes, “creates an opportunity for OEMs and component makers to create more products with greater variety.”

Hailey’s full piece is available now on EBN Online.

Marco Hogewoning, of the RIPE Network Coordination Centre (RIPE NCC), has taken on the topic of regulating the Internet of Things (IoT) in the UK – and highlights that “while there could be benefits […] there are also a lot of challenges.”

In a piece penned for Information Age, Marco paints a picture of a landscape showing an increase in both the quantity and severity of attacks – including attacks making use of IoT connections and devices. Against this background, Marco discusses the potential for regulation – in particular, the appointment of an IoT-specific regulator for the UK – and makes some interesting points.

“With greater awareness of IoT vulnerabilities and their potential impact, there are many ongoing discussions regarding the need for regulation,” Marco writes. “While there could be benefits to that approach, for instance, levelling the playing field between industry actors, there are also a lot of challenges. In the borderless world of the Internet, for regulation to have an effect, it needs to be internationally coordinated and that makes the process slow and complex. It will remain an uphill battle for regulation to keep pace with a rapidly evolving threat landscape and novel IoT applications that are being invented every day.”

At the same time, Marco points to “an increase in coordination and the adoption of self-regulatory approaches such as the Code of Practice” as having the potential to “turn the tide” without regulation, and also reminds consumers that “security remains dependent mainly on the user to check for and install updates regularly and to change any default passwords as soon as they unwrap their latest gadget” – something the industry needs to work on making easier for the less technical consumer.

Marco’s full piece is available now on Information Age.

The RISC-V Foundation has issued a call for speakers ahead of the RISC-V Workshop Zurich, scheduled for mid-June 2019, with a submission deadline of the 28th of February.

Hosted by the non-profit RISC-V Foundation in partnership with Informa’s Knowledge & Networking Division, KNect365, the RISC-V Workshop Zurich is to be held at ETH Zürich on the 11th to 13th of June 2019 as one of several events around the globe dedicated to the promotion of the free and open source instruction set architecture (ISA) and implementations thereof.

“The microprocessor IP market is being disrupted, and RISC-V is fast gaining support as an attractive license-free approach to architecture,” the Foundation explains in support of the event. “This open standard collaboration will transform and reshape established world order of the silicon market, and the implications of this change will resonate from Silicon Valley to Silicon Fenn and beyond.”

The event can’t take place without presenters, however, and the Foundation has issued an official call for participants to speak or run poster sessions at the event. Those interested have until the 28th of February to apply, while speakers selected for participation will be notified in early March.

More information on the RISC-V Workshop Zurich can be found on the official website, while those interested in presenting at the event can submit a proposal using the Foundation’s form.

Finally, the Design and Verification Conference (DVCon) 2019 is to host a panel on the verification and compliance implications of open instruction set architectures (ISAs) like RISC-V, organised by industry expert Imperas.

Dubbed “Verification and Compliance in the Era of Open ISA – Is the Industry Ready to Address the Coming Tsunami of Innovation,” the panel is to be organised by Imperas’ Larry Lapides, moderated by Tirias Research’s Kevin Krewell, and feature Andes Technology’s Emerson Hsiao, Breker Verification Systems’ Adnan Hamid, Facebook’s Rob Shearer, and Imperas’ Simon Davidmann as panellists.

The panel marks the first such discussion on the implications of open ISAs, which are seeing increased commercial adoption across a broad range of market segments, in the 31 years of DVCon history – a clear testament to the fact that open ISAs are leaving academia, and in some cases garages, and becoming a force to be reckoned with in the industry as a whole.

DVCon 2019 takes place on the 25th to the 28th of February in San Jose, California, with the Open ISA panel scheduled for the 27th of February between 0830 and 0930. Imperas has also confirmed it will be demonstrating its virtual platforms for embedded software and systems development, debug, and test at the event, with more details available on the official website.