The Things Network, the community-driven LoRaWAN project, has announced a world record successful transmission distance from the Servet project: 476 miles, or 766 kilometres.

Designed for low power yet wide area use, LoRaWAN is the technology behind community-driven wide-area networking project The Things Network – the largest open LoRaWAN network in the world, operating in over 100 countries. The Servet project, meanwhile, is a citizen science initiative focused on experimentation through weather balloons – and this month seven new balloons with The Things Network connectivity, alongside standard LoRa and APRS, were launched to set a new world record.

Jose Manuel Cuesta’s balloon-borne probe, fitted with three 3D-printed Moxon antennas and a reaction wheel for stabilisation, was the first to break the existing world record for LoRaWAN transmission distance with a 741 kilometre successful transmission; Enrique Torres’ Diana 1 probe quickly beat the newly-set record with one of its own at 766 kilometres, or 476 miles – despite having failed to reach its target altitude due to weather conditions. The theoretical maximum transmission distance for a LoRaWAN node, meanwhile, is estimated at 800 kilometres.

A full write-up of both records can be found on The Things Network’s blog.

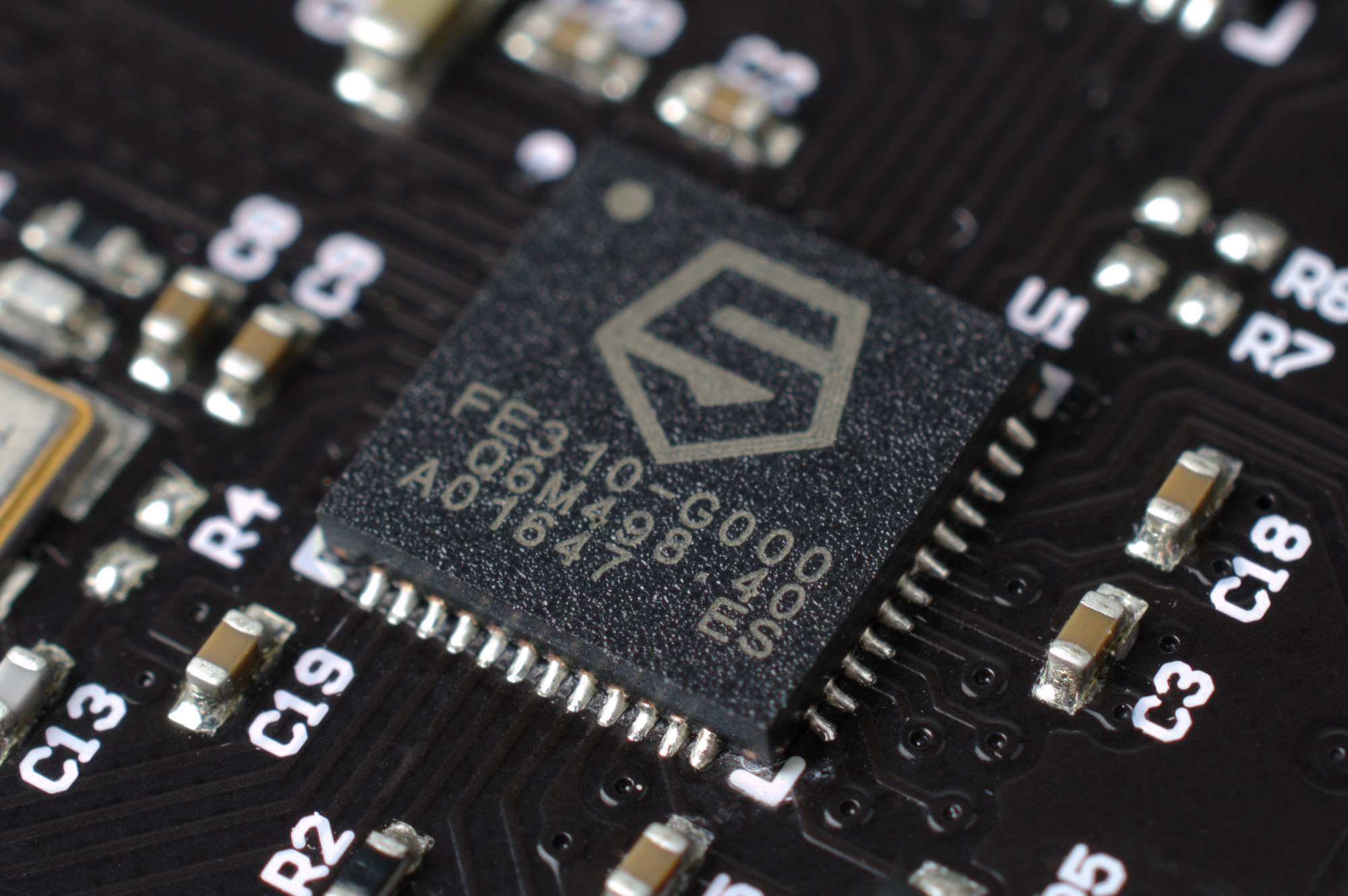

Alibaba, via the Pingtouge (T-Head) division of its DAMO Academy, has announced what it claims is the world’s most powerful processor based on the open RISC-V instruction set architecture (ISA): a 16-core 2.5GHz design built on a 12nm process node, dubbed the CoreXuanTie910 or XT910.

“The breakthrough is more than a mere performance enhancement of RISC-V processors. It means more IoT areas that require high-performance computing such as 5G, AI, networking, gateway, self-driving automobile, and edge server can now be powered by this latest RISC-V processor, which was previously used for simple embedded devices like smart-home appliances,” claims Jianyi Meng, senior director at Alibaba Group and lead developer on XT910, of his company’s new design. “We are excited about this new development and the exciting future that it unfolds for the RISC-V community.”

“We are truly fascinated by the important milestone that Alibaba’s RISC-V processor has created,” adds Calista Redmond, chief executive of the RISC-V Foundation. “We believe many chip developers can benefit from this technology breakthrough, which also helps accelerate the growth of the RISC-V community now that more IoT areas can be explored. I believe the RISC-V community, especially the community in Asia, will be on a much faster growth trajectory in the years ahead.

The XT910 is a 16-core 2.5GHz RV64GCV design on a 12nm process node with an additional 50 extended instructions designed to improve performance for arithmetic operations, memory access, and maintenance of cache and buffers. The source code for an XT910 simulator and emulator will be released in September, Meng confirms, though the company has not yet stated under what licence it will be made available – and neither has it said whether the part will be used wholly internally or if it plans to offer it as a commercial product.

“By sharing the simulation and emulation code, we hope to provide global developers with access to the high-performance processor so they can leverage the technology to develop prototypes for their own chips,” says Meng. “As a result, more innovation in IoT and AI fields can be created. That is aligned with Alibaba DAMO Academy’s mission of making technology more inclusive, open and accessible.”

The chip announcement is notable for the short timescale of its development: T-Head was founded less than a year ago, with the September release of the simulator and emulator code timed to celebrate its first birthday. Alibaba itself, meanwhile, has announced it is joining the CHIPS Alliance industry group, alongside its existing membership of the RISC-V Foundation.

Andes Technology has announced explosive demand for its proprietary processor cores based on the open RISC-V instruction set architecture (ISA), highlighting the growing demand for alternatives to x86, Arm, MIPS, and other proprietary ISAs.

Born from the University of California at Berkeley in 2010, the open RISC-V instruction set architecture (ISA) is as permissive as it gets: The licence under which the ISA is made available has no requirement that derivative products be made open-source in turn, and while many RISC-V cores are permissively licensed themselves there’s nothing to stop companies developing proprietary cores based on the open ISA – and that’s exactly what Andes Technology offers its customers, boasting of increasing demand that has seen 60 licensing agreements signed in the first half of 2019 alone.

“The growth of the RISC-V market is only in its infancy,” claims Andes’ president, Frankwell Jyh-Ming Lin, of the market’s growth. “Our customers’ applications are very diverse and include AI, IoT, ADAS, Netcom and consumer electronics. Customers choose Andes RISC-V solutions because of the technical support of its RISC-V products line, friendly interface and excellent products and solutions. Andes will continue to invest in developing RISC-V related products and environment, and work together with customers and partners to win new business opportunities.”

Just because Andes’ cores are themselves proprietary, however, doesn’t mean the company isn’t involved in the free and open source silicon movement in a positive manner. “Andes supports the technical and marketing committees of the RISC-V Foundation,” chief technology officer Charlie Hong-Men Su explains, his company having joined the Foundation in 2016. “In addition to contributing to the core technology and cooperating with the world’s major companies to develop the RISC-V architecture, Andes leads the latest trends in RISC-V technology.”

Andes has specifically called out China as an area of growth, with the government supporting the development of RISC-V applications in the region – thanks in no small part to an ongoing trade war with the US which has seen a major Chinese company, Huawei, cut off from Arm-based processor technologies.

CHIPS Alliance has launched a system-on-chip (SoC), built using Western Digital’s open-source SweRV Core and the FuseSoC build toolset, dubbed SweRVolf

A collaboration between FuseSoC creator and maintainer Olof Kindgren, Western Digital Director of Next Gen Platforms Tech Zvonimir Bandic, outgoing chief technology officer Martin Fink, and CHIPS Alliance, SweRVolf is a functional system-on-chip (SoC) design built around WD’s open-source SweRV EH1 RISC-V core. The design also builds on contributions from elsewhere in the free and open source silicon community.

“The idea is to offer a portable and extendable SoC for FPGA and simulation to experiment with the SweRV EH1 core,” award-winning engineer Kindgren explains. “Initially targets the Digilent Nexys A7 FPGA board and simulations with Modelsim or Verilator. Using FuseSoC this can quickly be ported to other targets too.

“This is also a testament to the vibrant FOSSi ecosystem as it combines IP cores and tools from many different developers and groups around the world to create a fully open source project that can be used in industry, academia or by curious hobbyists. To give some examples, apart from Western Digital’s CPU most AXI infrastructure comes from PULP Platform, DDR2 controller from Enjoy Digital, OpenOCD integration by M Labs, and others. Debug IF leans on lowRISC work, my very own FuseSoC and many more.”

The SoC launch, files and details for which are available on the CHIPS Alliance GitHub repository, comes as long-time RISC-V supporter and Western Digital chief technology officer Martin Fink announces his retirement. He is to be replaced by Dr. Siva Sivaram in the newly-formed role of President of Technology and Strategy, but will remain with the company in an advisory capacity for “matters relating to data centre architectures, including RISC-V.”

Researchers at the Delft University of Technology have published a roadmap which seeks to maximise the potential of the open RISC-V instruction set architecture (ISA) for space applications across the full range of requirements from low-power microcontrollers up to high-end payload processors for artificial intelligence applications.

“This paper proposes a roadmap to address present and future needs in space systems with RISC-V processors,” Stefano Di Mascio, Alessandra Menicucci, Eberhard Gill, Gianluca Furano, and Claudio Monteleone explain in the abstract to their paper, Leveraging the Opennes and Modularity of RISC-V in Space. “RISC-V is an open and modular instruction set architecture, which is rapidly growing in popularity in terrestrial applications.

“To satisfy different applications with contrasting requirements in satellite data systems, four different types of processors are identified: 1) low-area/low-power microcontrollers, 2) on-board computers, 3) general-purpose processors for payloads, and 4) enhanced payload processors for artificial intelligence. Several solutions based on RISC-V are proposed for each of these types of processors and compared with proprietary commercial-off-the-shelf and space-grade solutions. An extensive analysis of the results available from literature is conducted to show that RISC-V has the potential to solve such a wide range of needs.

“This paper will also show the unprecedented number of open-source implementations and models that were developed in a relative short time on a single instruction set architecture. Future space systems could benefit from many of those developments, and this work identifies and highlight what is still missing to satisfy the specific needs of processors for space, especially in terms of fault tolerance and technology readiness level.”

The full paper, which was supported by the European Space Agency (ESA), open-silicon-in-space pioneer Cobham Gaisler AB, and the Delft University of Technology, is available on the Aerospace Research Central website.

GigaDevice, a company which has previously concentrated on microcontrollers built around the proprietary Arm instruction set architecture (ISA), has released a new part based on the open RISC-V ISA: GD32V.

First spotted by RISC-V pioneer Sipeed late yesterday, the GigaDevice GD32V is based on the Nucleisys N20x RISC-V core, itself a commercialised variant of the LicheeTang E203 RV core, running at 108MHz with 8KB to 16KB of SRAM and 16KB to 128KB of flash memory. Each model is based on 3.3V input/output (IO) logic, but with 5V tolerance, and includes USB On-The-Go and CAN 2.0B peripherals.

According the launch presentation, shared in full on CNX Software, the new microcontroller offers a 15 percent performance boost in the Coremark benchmark compared to the company’s early Arm Cortex-M3-based GD32 microcontroller while consuming between 25 and 50 percent less power.

GigaDevice itself has yet to update its English-language website with details of the new chip, which is understood to be pin compatible with the earlier Arm-based GD32, but CNX has tracked down order pages for the microcontroller which reveal identical pricing to the Arm equivalents. Two low-cost development boards based on the chip have also been spotted: the GD32VF103C-START at $11 and the GD32VF103C-EVAL at $46.

The open-source QEMU machine emulator and virtualiser has received enhanced support for the open RISC-V instruction set architecture (ISA) in its 4.1.0 release.

Following on from the 4.0.0 release back in April, QEMU 4.1.0 brings a range of improvements to its support for the open RISC-V ISA. Chief among these are the definition of a new “spike” machine, the release of which officially deprecates older machines.

Other improvements include the first support for the RISC-V Privileged Specification 1.11.0, support for SiFive’s general-purpose input/output (GPIO) controller, the ability to make single steps over branches and jumps, correct handling of compressed illegal instructions, bug fixes in the 32-bit syscall application binary interface (ABI), and a cpu-topology device tree node on targets which support such trees.

The latest release also brings with it bug fixes and new features for other architectures, including Arm, MIPS, PowerPC, S390, SPARC, Tricore, x86, and Xtensa, full details of which are available in the changelog.

QEMU 4.1.0 itself can be downloaded from the official website.

IBM’s OpenPOWER Foundation, set up to build the POWER architecture ecosystem, has made a milestone announcement: it is to make the POWER instruction set architecture, along with key hardware designs and supporting technologies, available under an open source licence.

Announced along with the news that the OpenPOWER Foundation is to join the Linux Foundation, the release of the POWER instruction set architecture under an open licensing model marks a major boon for the free and open source silicon (FOSSi) ecosystem – while putting it in direct competition with relatively young upstart RISC-V.

“By moving the POWER ISA under an open model – guided by the OpenPOWER Foundation within the Linux Foundation – and making it available to the growing open technical commons, we’ll enable innovation in the open hardware and software space to grow at an accelerated pace,” explains OpenPOWER Foundation executive director Hugh Blemings. “The possibilities for what organisations and individuals will be able to develop on POWER through its mature ISA and software ecosystem will be nearly limitless.”

“We’ve heard in the past that developing a full featured core like POWER can be complicated – but that’s not necessarily the case. In fact, we believe the open source community can leverage the contributions made by IBM rather quickly. In addition to open sourcing the POWER ISA, IBM is also contributing a newly developed softcore to the community. In a very short time, an IBM engineer was able to develop a softcore on the POWER ISA, and get it up and running on a Xilinx FPGA. This softcore implementation is being demonstrated this week at OpenPOWER Summit North America.”

“As the chairman of the OpenPOWER Foundation Board of Directors, it’s an honour to share in such a tremendous moment with our community,” adds Artem Ikoev. “The opening of the POWER ISA and alignment of the OpenPOWER Foundation with the Linux Foundation is a reflection of our mature, sustainable and growing ecosystem. These changes will result in more consortia-driven initiatives and allow more diverse, innovative products and solutions to be brought to market.”

As well as the ISA itself, IBM has contributed reference designs for OpenCAPI and the Open Memory Interface (OMI). More information is available from the official announcement.

Finally, the Free Software Foundation Europe (FSFE) has announced the release of REUSE 3.0, a copyright and licensing specification and supporting utility designed to make license compliance as simple as possible for free and open source projects.

“The licensing of a software project is critical information,” explains FSFE’s Carmen Bianca Bakker and Max Mehl. “Developers set the terms under which others can reuse their software, from individuals to giant corporations. Authors want to make sure that others adhere to their chosen licenses; potential re-users have to know the license of third-party software before publication; and companies have to ensure license compliance in their products that often build on top of existing projects. The REUSE project, led by the Free Software Foundation Europe (FSFE), helps all of these parties.”

The core of REUSE is a specification that details where copyright and licensing information should be stored, and in what format. This data is then accessible using a tool – reuse – which reads the data and pulls up a summary detailing any code that has bad or entirely missing licensing information attached, any licences referred to but not actually used, and highlights the licences used in a given project along with marking files that have valid license and copyright information.

“The REUSE initiative will continue its work on making copyright and licensing easier for everyone,” the pair add of the project’s future. “Our roadmap includes configurable templates for adding the headers with the helper tool, as well as an API that for example allows projects to display a dynamic badge indicating the REUSE status, or third-party services to integrate REUSE checks.”

More information on REUSE 3.0 can be found on the FSFE blog, while a step-by-step tutorial guides developers and publishers through making their projects REUSE compliant.