AB Open’s Andrew Back has written up a project to create a bat detector with LoRaWAN connectivity, transmitting data on bat call measurements via The Things Network using MQTT.

“When ODI Leeds recently said that they were interested in LoRaWAN-enabled bat detection, we thought, ‘What a fun idea, let’s have go!’,” writes Andrew of the project, which features an Arrow SmartEverything LION microcontroller and LoRa module connected to an ArduBat shield designed by Tony Messina and Frank Pliquett. “In this post we take a look at a first prototype put together by a colleague and myself and which, in the great open source tradition, builds on the work of others.”

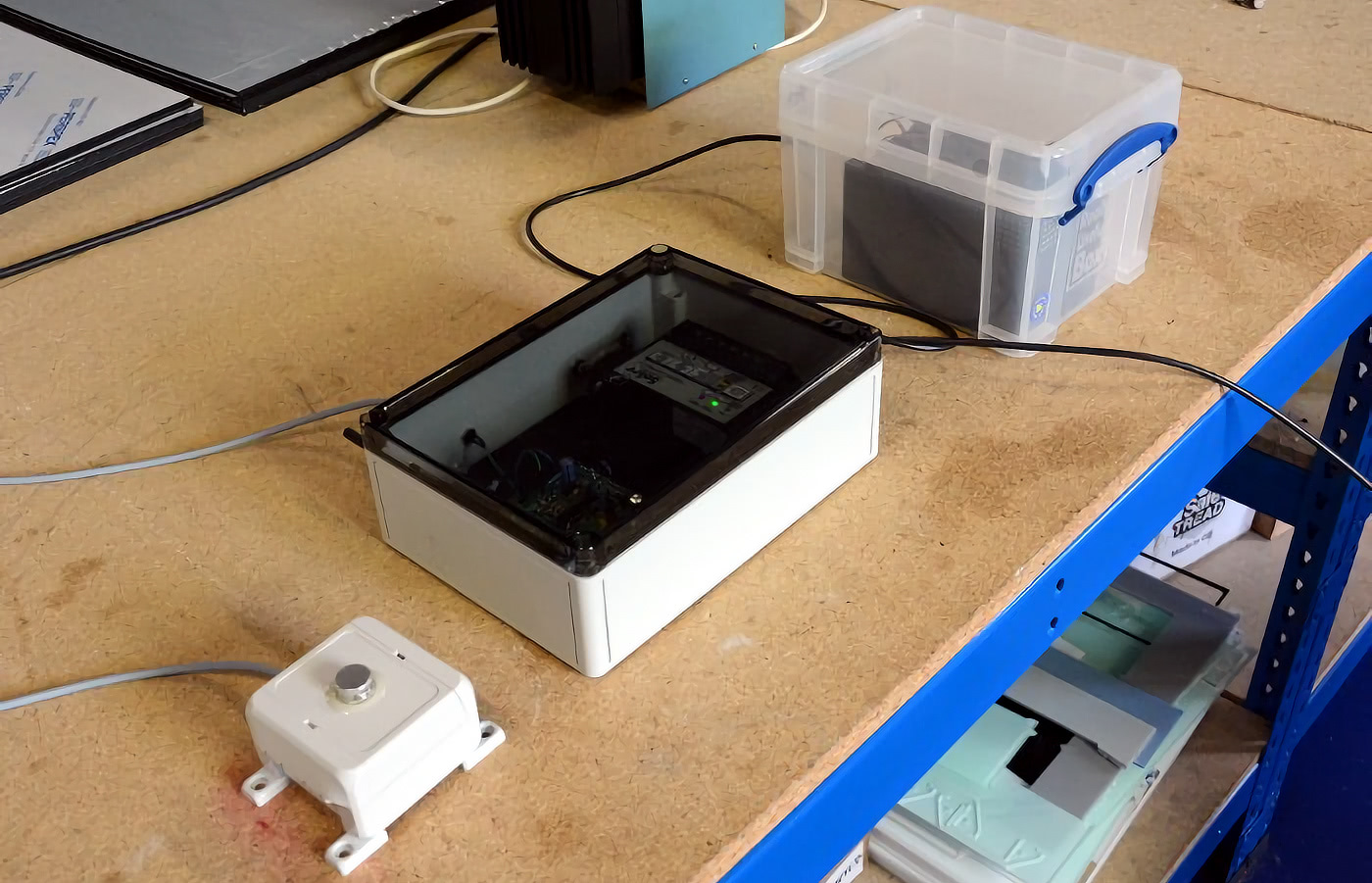

The project was complicated by a simple truth: bats don’t tend to live inside dry buildings with stable power supplies and handy Wi-Fi. A LoRaWAN connection to The Things Network handles the latter problem, while the former issues were solved using a solar panel, lead-acid battery, and clever casings for water ingress prevention.

All About Circuits’ Chantelle Dubois has published a handy roundup of some of the biggest RISC-V projects currently underway – including some you’ll have read about here in AB Open’s CRU.

In Chantelle’s roundup, which is based on presentations made during the Hot Chips 2017 conference, a range of interesting projects are highlighted: the partnership between SiFive and Rambus, detailed in an earlier CRU; the Celerity system-on-chip designed by researchers from the Universities of Michigan, Cornell, and California at Los Angeles (ULCA), which packs a total of 501 RISC-V cores in its design alongside a computer-vision focused neural network processor running at 625MHz; Codasips’ Berkelium family of RISC-V implementations, the latest Internet of Things (IoT) targeted version of which was highlighted in an earlier CRU; and the Gray Research RISC-V RV (GRVI, pronounced ‘groovy’) Phalanx, featuring softcore processors and accelerator cores designed to boost field-programmable gate array (FPGA) performance.

Remaining on a RISC-V topic, Electronic Design’s James Morra has published an an interview with SiFive’s new chief executive Naveed Sherwani on the topic of opening a chip design factory.

The most promising part of the interview for those interested in the success of RISC-V in general comes from Naveed’s claims as to the level of interest the company is seeing: “We have heavy customer demand right now,” Naveed reveals during the interview. “We have three or four meetings with big corporations every day and none of them are set up by us.”

For a relative newcomer instruction set architecture attempting to break into markets which had previously been considered all-but sewn up by the likes of ARM, MIPS, Intel, and AMD, that’s a strong indicator that the RISC-V movement as a whole is heading in the right direction.

For those interested in RISC-V on a smaller scale, Michael Welling has designed a compact, breadboard-compatible open-hardware development board based on SiFive’s Freedom FE310 microcontroller.

Published under the CERN Open Hardware Licence v1.2, Michael’s design breaks out the pins of the RISC-V-based Freedom FE310 microcontroller and includes micro-USB connectivity for power and data purposes. While SiFive has its own range of development boards based on the Freedom family – including the HiFive1 we reviewed earlier this year – Micheal’s version has the benefits of being extremely compact and able to plug directly into the top of a solderless breadboard with no additional wiring, not to mention its permissive licence status.

Those struggling to build the newly RISC-V compatible GNU Compiler Collection (GCC) with binutils and newlib will likely find the lowRISC project’s guidance invaluable – though the project warns its instructions are suited more to testing than deployment.

“There are a number of available options for building a RISC-V GCC toolchain. You might use the build system from the riscv/riscv-tools repository, or investigate toolchain generators such as crosstool-ng. However in the case of riscv-tools, it’s not always clear how this corresponds to the code in the relevant upstream projects,” the latest lowRISC blog post explains. “When investigating a potential bug, you often just want to build the latest upstream code with as little fuss as possible. For distribution purposes you’d probably want to perform a proper multi-stage build, but for a quick test you might find the following recipe useful.”

The list of instructions on the lowRISC blog will build a newlib toolchain targeting the 32-bit RV32IMA, with the GCC files taking precedence over duplicates from newlib and binutils generated during the build process.

The registration process for the seventh annual RISC-V Foundation Workshop has officially opened, ahead of the event itself at the end of November.

Organised by the RISC-V Foundation and hosted by Western Digital in Milpitas, California, the seventh annual workshop is spread over three days: Tuesday and Wednesday the 29th and 30th of November will feature presentations from the RISC-V community with a demo reception on Tuesday evening, while on Thursday the 30th of November a series of closed events is being held exclusively for members of the RISC-V Foundation itself.

“Please register early as all of our previous workshops have sold out and seating is limited,” warns RISC-V Foundation executive director Rick O’Connor. “Registration will close on Tuesday November 14, 2017.”

Anyone interested in deep neural networks (DNN) should be following the announcements from Intel subsidiary Movidius closely: the company has released a low-power USB-connected Vision Processing Unit (VPU) co-processor and promises a coming future release with ten times the performance.

Based on the Myriad 2 co-processor developed by Movidius prior to its acquisition by Intel, the Neural Compute Stick offers in excess of 100 gigaflops of compute performance in a 1W power envelope connected to the host system via USB. That performance can then be harnessed for deep neural network (DNN) and computer vision acceleration using popular frameworks including Caffe.

Its successor, though, promises still more: the Myriad X VPU, Intel has claimed, offers a tenfold increase to more than a teraflop of compute performance in the same power envelope – though the company has been thus far silent on when the upgraded chip will appear in a Neural Compute Stick successor.

Version 4.13 of the Linux kernel has been officially released by Linus Torvalds, bringing a range of improvements and enhancements of interest to embedded systems developers.

CNX Software has gone through the 4.13 changelogs to pull out the most interesting developments for Linux on ARM and MIPS platforms, which include: power management integrated circuit (PMIC) support for the NextThingCo CHIP and CHIP Pro development boards and compatible designs, support for the Rockchip input-output memory management unit (IOMMU) driver on 64-bit ARM platforms, support for the Rockchip RK3328 and its accessories in the device tree, fixes for general-purpose input-output (GPIO) on Samsung’s Exynos platforms, better error handling in Qualcomm’s Shared Memory State Machines (SMSM), and support for queued read/write locks and spinlocks on MIPS platforms.

As always, the latest Linux kernel is available from the Linux Kernel Archives.

Finally, the Ohio Supercomputer Centre has announced the release of Open OnDemand 1.0, an open-source platform designed to allow high-performance computing (HPC) centres to more easily offer their resources out for use.

“Up until this point, clients had to install software, use a cryptic file editor and learn batch system commands,” claims David Hudak, interim executive director of OSC, regarding the project. “Our objective with the Open OnDemand project has been to build a portal that will allow them to use HPC without a big learning curve. It’s about lowering the barrier of entry to the world of supercomputing.”

Open OnDemand has previously been in beta status, with around six centres installing and deploying the package for general use and a further six in the process of testing and evaluating the platform. “With 1.0, we feel that Open OnDemand now enables our peer HPC centres to provide to their clients with simple, easy access to powerful computing services,” adds Basil Gohar, manager of the OSC Web and Interface Applications Group. “All they need is a web browser, their username, and password.”

The software is made available under the MIT Licence from the OSC GitHub repository.