AB Open and its hardware division Ground Electronics have launch a campaign for Circumference, a family of custom-designed desktop cluster computing units based around the popular Raspberry Pi and UDOO x86 single-board computer families.

Available to pre-order now on crowdfunding site Crowd Supply, the Circumference C25 boasts support for up to eight Raspberry Pi computers while the Circumference C100 can hold up to 32 giving it a total maximum capacity of 128 64-bit low-power Arm processing cores and 32GB of RAM. Both units include a UDOO x86 control node, known as the Front-End Processor (FEP), and a custom electronic backplane system designed by Ground Electronics – creating the first truly standalone Raspberry Pi cluster solution on the market.

“The complexity of application architectures is ever increasing, with components spread across multiple servers, virtual machines, containers, and increasing making use of advanced systems for dynamic deployment, scaling, and management,” explains AB Open’s Andrew Back of the project. “While development, testing, and education in such applications is sometimes possible using virtual machines, it doesn’t provide quite the same environment or hands-on experience as using multiple physical host machines. The Circumference solves this problem, offering a fully-functional compute cluster in an attractive box that doesn’t look out of place on your office desk or draw masses of power to run.”

Featuring integrated and user-controllable power and network distribution, each Circumference is fully user-controllable through a command-line interface or application programming interface (API) running on the Front-End Processor or any host on the same network. The clever backplane design makes for easy hardware installation and maintenance, while the attractive housing serves as both an eye-catching design statement and protection for the hardware inside. The C100 also includes a front panel module, based on Arduino technology, for user-programmable at-a-glance status monitoring.

The campaign sees the Circumference C25 priced at $549 for the first 25 Early Bird pledges rising to $599 when these are gone, representing a $50 discount over the campaign general pricing, and the C100 priced at $2,599. Each unit includes all the custom hardware and cabling required for cluster operation, including the backplane and network switches, requiring the user to supply only the Raspberry Pi and UDOO x86 boards, storage, and a power supply. The C25 is also available in an Early Access tier, which will be shipped two months earlier than the general tiers.

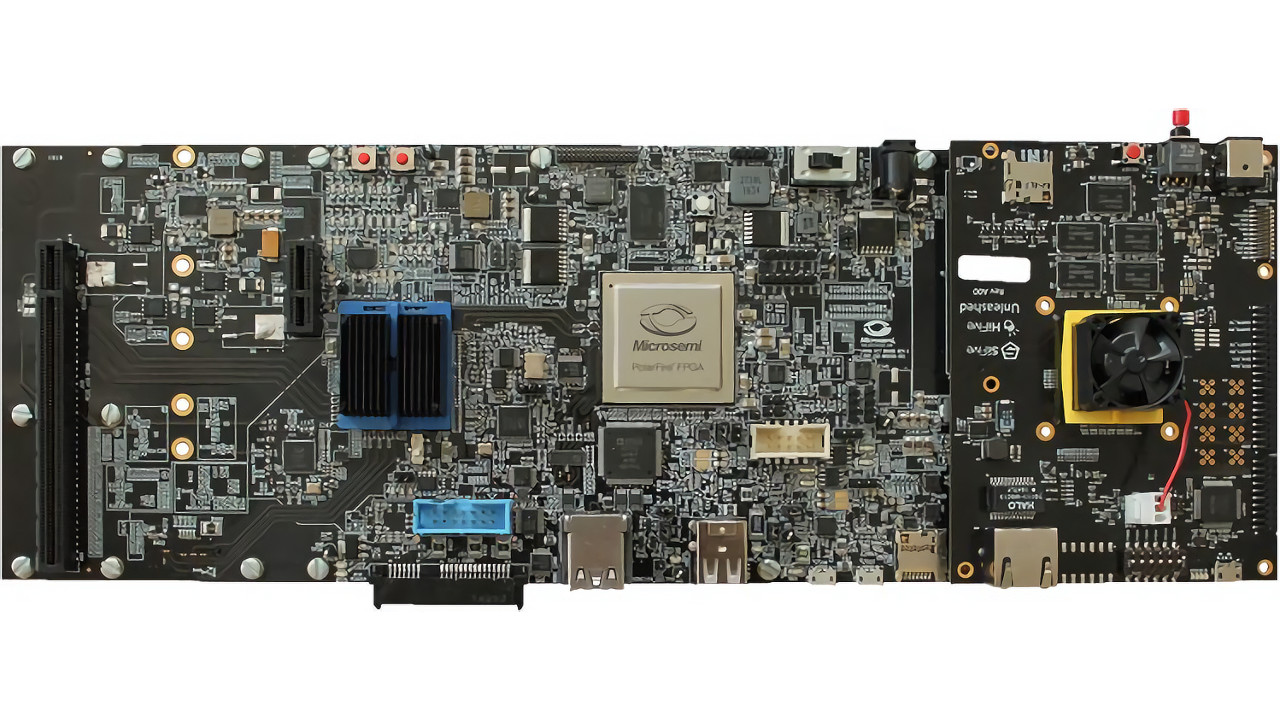

The world’s first Linux-capable RISC-V development board now benefits from an expansion that adds PCIe, M.2 SSD, SATA, HDMI, a 300K element PolarFire FPGA, and more.

Launched back in February at FOSDEM the HiFive Unleashed RISC-V development board boasts a 64-bit Freedom U540 SoC with features that include a 4+1 Multi-Core Coherent Configuration (up to 1.5 GHz), implemented in TSMC’s 28nm process. The development board also has 8GB DDR4 RAM, a USB UART for console, gigabit Ethernet, Micro SD storage, and FMC expansion.

Previously if you wanted to add PCIe peripherals — which also includes USB devices via a PCIe/USB adapter — it was necessary to use a Xilinx VC707 FPGA development board plus FMC PCIe Root module at a combined cost approaching $5,000. However, this has now dropped to $1,999 thanks to a custom expansion board from MicroSemi announced earlier this week.

The $1,999 price also includes a free one year Libero Gold License, which is required if you want to synthesize your own FPGA designs. At the time of writing a bitstream is provided that enables a PCIe Root Complex, although it is stated that in future the kit will be opened up to custom solutions, such as implementing your own application-specific hardware accelerators, for example.

Limited expansion boards and bundles that include a HiFive Unleashed are being made available via Crowd Supply and orders placed now are scheduled to ship at the end of the month.

Colombia-based semiconductor specialist OnChip has announced a 32-bit RISC-V microcontroller design aimed at low-power sensor applications, developed in partnership with SiFive.

Fresh from announcing the next generation of Itsy-Chipsy, the company’s low-quantity semiconductor fabrication platform which aims to allow the creation of single-unit DIP-packaged chips for around $100, OnChip has shown off the design of a new microcontroller part based on a 32-bit implementation of the RISC-V instruction set architecture and positioned firmly at the low-power sensor market.

“Thrilled to announce a 32-bit MCU, RISC-V based, with low-power always-on peripheral enabling low power sensor applications for open-source silicon,” the company wrote in its announcement on social networking site Twitter. “Have a good trip Open-V, our most recent work with SiFive has been sent to fab.”

An image accompanying the announcement, reproduced above, shows a part featuring a true random number generator, 12 and 10 bit digital to analogue (DAC) and analogue to digital converters (ADC), and a brownout detector for save use in low-power and unreliable-power situations.

Part of the company’s Open-V project, about which more information is available on the company’s website, the OnChip-SiFive collaboration does not yet have a release date.

The Parallel Ultra-Low Power (PULP) Project has celebrated its fifth birthday with a retrospective, discussing the progress made since its inception during a meeting at the University of Bologna in May 2013.

“It has been exactly 5 years since Luca Benini started the PULP (Parallel Ultra Low Power) project in a meeting attended by a handful of people squeezed in a tiny office in the University of Bologna,” writes Frank K. Gurkaynak, director of the Microelectronics Design Centre at ETH Zürich, in the retrospective piece published to business networking platform LinkedIn. “We are very proud that our work is finding applications and recognition in the ‘real world,’ and has proven itself to be more than ‘a toy that academics play with.’

“In the 5 years since we launched the PULP Project, we have developed and tested more than 20 ASICs [Application Specific Integrated Circuits] in various technologies. We are expecting our latest chip, Poseidon, in Globalfoundries 22FDX technology back from manufacturing any moment. The HDL code for the PULP based blocks used in this chip is already available for everyone to use on our GitHub page (just to clarify: at the moment licensing restrictions allow us to provide only HDL code), giving everyone who is interested access to silicon proven IP.

“There are still many skeptics of the open source hardware movement, and I will not be able to convince everyone that open source hardware has a future. However I can tell you that, as the main PULP development team at ETH Zurich and University of Bologna we are committed to continue to support high-quality open source hardware and we are in discussions on participating several exciting projects that we hope to be able to announce soon.”

More information on the PULP Project and its release can be found on the official website.

IEEE Spectrum, the magazine of the Institute of Electrical and Electronics Engineers, has announced a webinar discussing the deployment of resilient network architectures for the Industrial Internet of Things (IIoT), to take place in June.

“A resilient, holistic network architecture can help create the secure, scalable and robust infrastructure needed to facilitate IT/OT [Information Technology/Operational Technology] convergence, reduce risks and maximise overall plant uptime,” explains host Gregory Wilcox, network and security specialist at Rockwell Automation, of his webinar’s topic. “But achieving IT/OT convergence requires an understanding of Layer 2 and 3 network topologies, resiliency protocols, managed and unmanaged switches, and numerous other network design considerations”

In furtherance of that understanding, Gregory’s webinar will cover tested and validated reference architectures and their documentation, best practices for the establishment of a resilient and robust network infrastructure, and how to determine the degree of resiliency and application availability required for a plant-scale implementation.

The free webinar, which will last an hour, is scheduled to take place on Wednesday the 20th of June 2018 at 1700 GMT. More information, and a registration link, is available on the official website.

The latest Osmocom Cellular Network Infrastructure (CNI) releases bring over 70 noteworthy updates to the free and open source field proven mobile stack.

As noted in a post back in March the Osmocom CNI stack has come a long way since the OpenBSC “network-in-the-box” which originally grew out of a hack to drive surplus BTS equipment. Having recently switched to a new decomposed architecture which brings far greater flexibility and will drive increased reuse, it appears that this is in heavy development with new features and fixes coming fast.

In a news item posted on the Osmocom CNI Redmine yesterday, Harald Welte notes how the “new tagged/released versions contain half a year of work since the previous versions released in early November 2017.” Going to to say “All-in-all, the post-NITB stack has gained a lot in terms of spec compliance, robustness, stability and features during this period.”

A total of 13 projects have received new releases, ranging from libosmocore — which as the name suggests sits at the foundations of many other projects — to OsmoSGSN, which is used to support GPRS networks.

Individual changes include those such as OsmoTRX gaining an interactive VTY interface — similar to that which OsmoBTS and OpenBSC have had for some time —and OsmoMSC closer adherence to 3GPP specifications, along with a whole host of stability improvements.

For further details and for links to the latest builds, see the Osmocom website.

Wireless semiconductor specialist Silicon Labs has published a summary of its recent long-term test into mesh network technology for the Internet of Things (IoT), putting Zigbee, Bluetooth Mesh, and Thread through their paces.

Designed to simplify the deployment and management of sensor networks, mesh networking allows each node in the network to communicate with each other node – meaning that vast swathes of sensors can be controlled and monitored through a very small number of gateway nodes. As with any technology, there are competing standards; Silicon Labs’ test aims to figure out which of the three most popular is the most effective.

In a write-up for EE Times, Silicon Labs’ Tom Pannell explains: “We conducted the tests over a 12-month period in a commercial Boston office building with active Wi-Fi and Zigbee networks in range. The wireless test clusters were deployed in hallways, meeting rooms, offices and open areas.”

The test’s conclusion, sadly, is not exactly clear-cut. “The fact is, there is no wining mesh protocol,” Tom explains, pointing to results which saw similar performance between technologies in small networks, Bluetooth lagging behind for larger networks and larger payloads but coming out on top for sub-11 byte messaging, and all suffering from latency increases as the network size grows. “Performance varies greatly based on the application requirements. The test results underscored several factors that are critical in making the right protocol choice.”

Tom’s write-up is available now on EE Times, while the full report and supporting webinar can be found on Silicon Labs’ website.

Finally, Intel has announced the launch of the OpenVINO toolkit, a visual inference and neural network optimisation engine designed with vision-based Internet of Things (IoT) development in mind.

“The OpenVINO toolkit is designed to enable users to fast-track development of high-performance computer vision applications, unleash deep learning inference capabilities across the entire Intel silicon portfolio, and provide an unparalleled solution to meet their AI [Artificial Intelligence] needs,” claims Intel’s Adam Burns of the release. “The new toolkit also includes three major APIs: The Deep Learning Deployment toolkit, a common deep learning inference toolkit that scales across Intel Vision Products, and optimised functions for OpenCV and OpenVX.”

Designed to tie in with Intel’s hardware platforms, including the Movidius Myriad family of vision processing units (VPUs) for which it recently launched a development support programme, the OpenVINO toolkit is capable of running on CPUs, GPUs, VPUs, and FPGAs – including on edge devices, the company promises.

More information on the OpenVINO toolkit, which was previously known as the Intel Computer Vision Software Development Kit (SDK), can be found on the official website.