The Free and Open Source Silicon Foundation has announced that ORConf 2018 will be held over the weekend of September 21st to 23rd in Gdansk, Poland.

Now in its seventh year, ORConf is a free-to-attend conference for open source digital, semiconductor, and embedded systems design engineers. What started as the annual OpenRISC developer conference has grown to become a broad open source digital design-oriented event, featuring talks on topics including RISC-V, OpenPiton, FPGA toolchains, EDA tools, and ASICs for makers, to name but a few.

Talk proposals are invited, there is an announce mailing list to stay informed, and those interested in finding out about sponsorship opportunities should contact the FOSSi Foundation.

Closer both geographically and temporally, on Thursday 22nd of March the BCS Open Source Specialist Group and Open Source Hardware User Group will host a free-to-attend event dedicated to the topic of open source software compliance in the supply chain.

The one-day event will explore freely available tools and methods to support open source software compliance efforts, featuring talks and hands-on workshops, with insights into practical experiences and lessons learned. While also dispelling the myth that FOSS compliance is an exercise that requires costly proprietary tooling and professional services.

This is a rare opportunity to hear from FOSS compliance experts and on numerous key open source initiatives. Definitely not to be missed if you have anything to do with embedded software development, or otherwise packaging and redistribution of open source software.

To find out more and to register see the event page.

Electronic Design is continuing its 11 Myths series, which covered LoRaWAN last month, with a look at the RISC-V open instruction set architecture (ISA).

“Many companies today are exploring free, open-source hardware and software as an alternative to closed, costly instruction set architectures (ISAs). RISC-V is a free, open, and extensible ISA that’s redefining the flexibility, scalability, extensibility, and modularity of chip designs. Despite its rich ecosystem and growing number of real-world implementations, there are misconceptions about RISC-V that have companies holding back from fully realising its benefits,” claims author Ted Marena, director of system-on-chip (SoC) and field-programmable gate array (FPGA) products at Microsemi Corporation, in his introduction to the piece.

Ted’s article covers a range of common misunderstandings regarding RISC-V, ranging from the mistaken belief that RISC-V is a purely academic undertaking to the efficiency of implementations, licensing considerations, and the ability or otherwise to port designs from an FPGA to an application specific integrated circuit (ASIC) for mass production.

The full article can be read over on Electronic Design now.

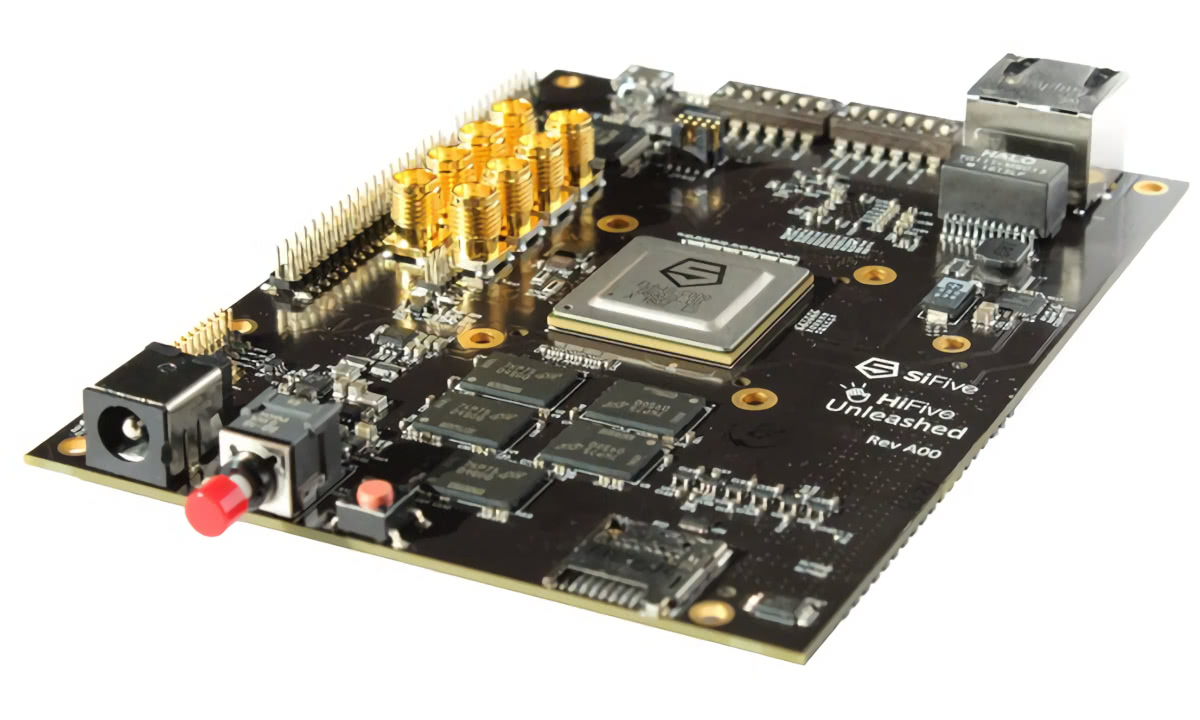

SiFive has demonstrated its RISC-V HiFive Unleashed single-board computer (SBC) at FOSDEM 2018 running Linux, presentation software, and a Quake port, with first boards to ship in around eight weeks time.

In a presentation entitled, Igniting the Open Hardware Ecosystem with RISC-V, we first heard from SiFive’s Palmer Dabbelt, who provided a background to RISC-V — including the motivations behind the architecture and illustrating why the ISA is the most important interface in a computer system — before going on to detail the current status of Linux on the free and open ISA.

After covering the specifications of the board – which include its four-plus-one multi-core configuration running at speed sof up to 1.5GHz, 8GB of DDR4 ECC memory, 32MB QSPI flash, gigabit Ethernet, and an FPGA Mezzanine Card (FMC) expansion header – SiFive chief technical officer Yunsup Lee revealed that the presentation itself was actually running on a HiFive Unleashed and next proceeded to give a quick demo of Quake running on the system. By way of proving that smoke and mirrors were not at play, a trolley was then wheeled out from behind the lectern, revealing a HiFive Unleashed and a PCI cage containing a graphics card.

For the purposes of the demo and developing early peripheral support, a Xilinx VC707 board is used to provide a PCI interface. In using this SiFive were able to reuse their U540 FPGA platform design, with the processor removed and in its place a ChipLink connection running between the two boards via FMC. However, SiFive are also working with MicroSemi to produce a dedicated peripheral expansion add-on board for the HiFive Unleashed.

The HiFive Unleashed is currently available to pre-order via Crowd Supply, with a total of 75x early access boards priced at $1,250, and standard pricing of $999 for end June shipping.

Bootlin, formerly known as Free Electrons, has launched a crowdfunding campaign to provide support for the Allwinner Video Processing Unit (VPU) in the mainline Linux kernel, for out-of-the-box hardware accelerated video decoding and encoding.

Found in many of Allwinner’s Arm-based system-on-chip (SoC) designs for embedded and low-power platforms, the Allwinner VPU provides hardware offload for video encoding and decoding – allowing the chip to save power by down-clocking the CPU during these otherwise processor-intensive operations. Unfortunately, as with many SoC designs, the VPU relies primarily on proprietary extensions to operate – leaving users with the choice of using customised kernels typically based on older releases or using the latest mainline Linux kernel but without support for the VPU.

Building on the work of Maxime Ripard and others, Bootlin is looking for funds to complete the work of creating full mainline kernel support for the Allwinner VPU, allowing devices based on the company’s SoCs to enjoy hardware-accelerated video decoding and encoding using the standard Linux kernel and no ‘binary blobs’ or other proprietary modifications.

At the time of writing the campaign had already surpassed its €17,600 goal with more than a month still remaining.

The Institute of Electrical and Electronics Engineers (IEEE) has published an interview with noted engineer Andrew ‘Bunnie’ Huang on the topic of how small teams can design custom silicon in a constrained budget.

“FPGAs [Field Programmable Gate Arrays] waste a large amount of silicon compared with an ASIC [Application Specific Integrated Circuit], so the cost floor, which depends in large part of the surface area of silicon required for the chip, is often an order of magnitude higher than you’d want it to be,” Bunnie explains of the reasons a small start-up may want to build custom silicon. “But fabricating an ASIC isn’t cheap either.

“There are some open-source tools that might be able to get you there. The ‘SCMOS‘ design rules are the most workable. As for design software, you can use an open-source toolchain based on Magic (Xcircuit, IRSIM, NetGen, Qrouter, and Qflow). All to say, down to around maybe the 180-nanometer technology node (or so), you could get away with using open-source tools. Smaller than that, though, requires doing really funny stuff with the mask imaging and using shapes that aren’t just simple polygons anymore. And the design kits from various vendors to accomplish that get more and more closed. 180nm is pretty ‘big’ by today’s standards. But if you really wanted to place some special combination of circuits on a single silicon die, you could do it this way. And it could lead to some novel products that would otherwise be impossible with discrete designs.”

The full interview is available on the IEEE Spectrum site now.

Finally Mozilla, the organisation behind popular open-source browser Firefox, has announced the release of a stable build of its Things Gateway, promoting its Internet-of-Things (IoT) focused Project Things initiative from a ‘hack’ to a launched – though early-stage – product.

Originally unveiled as a prototype back in June 2017 under the Mozilla Hacks engineering banner, the Things Gateway is an open-source platform which ties a front-end network interface into Mozilla’s Web Thing application programming interface (API) with a NodeJS back-end tied to the organisation’s Things Cloud platform. Designed to be compatible with ZigBee and Z-Wave wireless devices, the early prototype allowed for basic use-cases aimed at those eager to test its potential.

With this week’s release, though, the Things Gateway gains significantly more functionality including speech recognition and synthesis and a ‘rules engine’ for simple “if this, then that” logic. “We believe the future of connected devices should be more like the open web,” explains a Mozilla spokesperson of the company’s efforts. “The future should be decentralized, and should put the power and control into the hands of the people who use those devices. This is why we are committed to defining open standards and frameworks.”

The latest Things Gateway release is, Mozilla claims, the first to be accessible to anyone regardless of technical capabilities. A tutorial written by Mozilla’s Ben Francis walks through the installation and configuration of the software on a Raspberry Pi microcomputer, while more information is available on the company’s dedicated IoT site.