Amazon has announced that it has added support for the RISC-V open instruction set architecture (ISA) to the MIT-licensed FreeRTOS real-time operating system kernel.

“RISC-V is a free and open ISA that was designed to be simple, extensible, and easy to implement. The simplicity of the RISC-V model, coupled with its permissive BSD licence, makes it ideal for a wide variety of processors, including low-cost microcontrollers that can be manufactured without incurring licence costs,” Amazon’s Jeff Barr explains. “Development tools, including simulators, compilers, and debuggers, are also available.

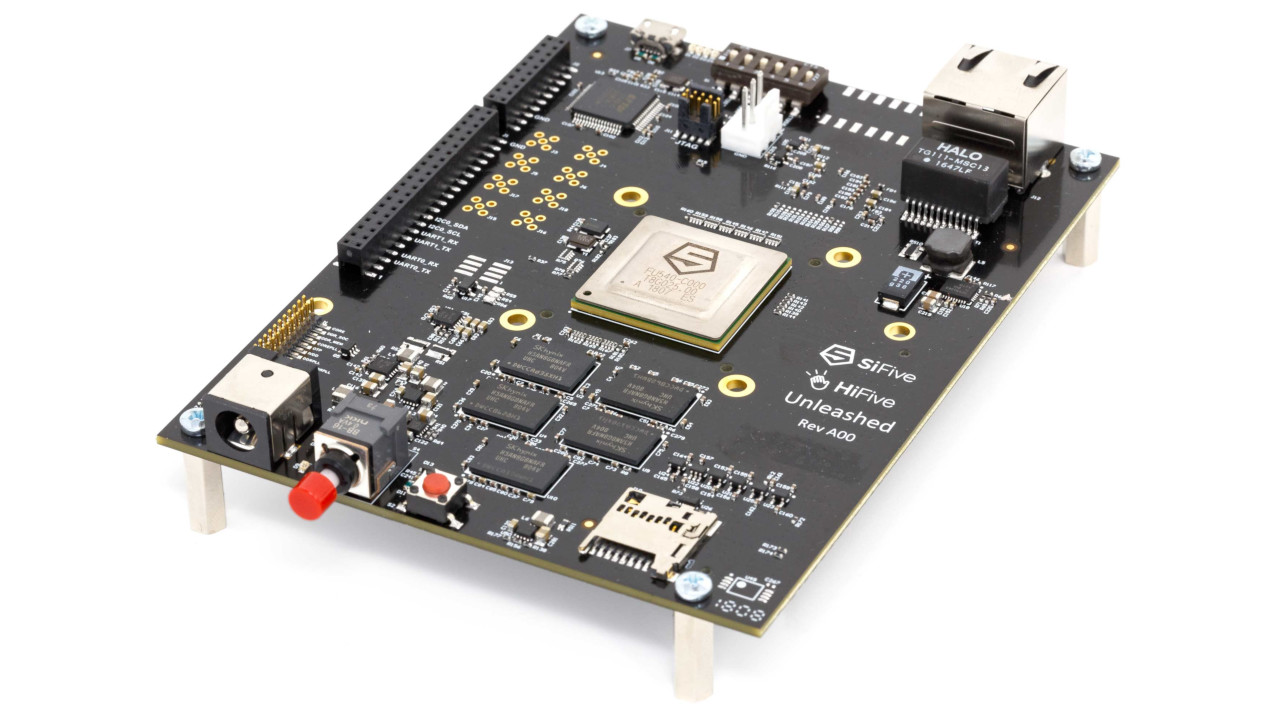

“Today I am happy to announce that we are now providing RISC-V support in the FreeRTOS kernel. The kernel supports the RISC-V I profile (RV32I and RV64I) and can be extended to support any RISC-V microcontroller. It includes preconfigured examples for the OpenISA VEGAboard, QEMU emulator for SiFive’s HiFive board, and Antmicro’s Renode emulator for the Microchip M2GL025 Creative Board.

“You now have a powerful new option for building smart devices that are more cost-effective than ever before!”

Amazon’s work on FreeRTOS, under the umbrella of its Amazon Web Services division, has seen it add a range of libraries focused on the Internet of Things (IoT), alongside support for Bluetooth Low Energy, over-the-air (OTA) updating, and Wi-Fi connectivity. The latest release, and more information, is available from the official website.

Imagination Technologies and Andes Technology have announced a partnership to combine the former’s Ensigma wireless intellectual property (IP) with the latter’s RISC-V N22 microcontroller IP in order to create an off-the-shelf product aimed at the Internet of Things (IoT) sector.

The collaboration between the two companies marks the first time Imagination has shown interest in the RISC-V market; previously, the company’s general purpose processing products had centred around the proprietary MIPS instruction set architecture (ISA) which it acquired in 2012 in a $100 million deal before selling it on for $65 million in 2017 – with eventual owner Wave Computing announcing it would make the ISA available royalty-free and with no licensing fee as the MIPS Open Initiative late last year.

The partnership will see Imagination providing low-power communications IP from its Ensigma division covering Wi-Fi, Bluetooth, IEEE 802.15.4, and Global Navigation Satellite System (GNSS); Andes, meanwhile, will provide its latest N22 microcontroller IP, based on the free and open source RISC-V instruction set architecture. The combined product will be made available as an off-the-shelf solution for home automation, health devices, location tracking, smart meters, security, wearables, and other IoT markets, the companies have confirmed.

“RISC-V is a compact, modular, and extensible architecture, which can be applied to many applications. The 2-stage pipeline N22 is the smallest RISC-V core in our V5 family but delivers an impressive performance of 3.93 CoreMark/MHz,” claims Andes’ president Frankwell Lin. “It also can reach over 750MHz at TSMC 28nm under worst case conditions. The combination of Andes’ industry leading RISC-V processor IPs with the wide range of connectivity IPs available from Ensigma, provides the ideal solution for many IoT markets.”

“By working with Andes, we are able to provide a comprehensive solution for customers creating connected RISC-V embedded devices,” adds Imagination chief Ron Black, “enabling them to get to market faster and with the knowledge that the solution is based on proven technology, already shipped in volume.”

The companies have not yet announced a launch date for their combined product.

GreenWaves Technologies, which launched the GAP8 RISC-V low-power processor and GAPuino development board in February last year, has announced that it has raised €7 million in Series A funding – a clear demonstration of the startling growth in the free and open source silicon (FOSSi) market.

“This support from a distinguished group of corporate investors demonstrates the GAP processor family’s unique value proposition within this emerging market,” claims Loic Lietar, GreenWaves co-founder and chief executive, of the investment from Huami, Soitec, and other unnamed investors. “We have been one step ahead of the market in identifying and serving this segment that is now widely recognised by the industry.”

Based on the work of the Parallel Ultra Low Power (PULP) Platform project, GreenWaves’ GAP8 was first demonstrated on a field-programmable gate array (FPGA) in March 2017 before landing as finished silicon less than a year later. The design includes an eight-core RISC-V computational cluster, integrated convolutional neural network (CNN) accelerator, and the promise of completing tasks including always-on face detection in a power envelope measured in milliwatts.

“We are very pleased to be participating in GreenWaves’ Series A financing round,” says Wang Huang, Huami chief executive. “GreenWaves’ GAP8 and strong product roadmap has set the bar for delivering energy efficiency for high performance signal processing and machine learning inference algorithms on edge devices, including wearables. We see a wide range of use cases for GAP8 processor that will transform IoT computing. This investment will also strengthen our portfolio in the RISC-V ecosystem.”

In the year since its launch, GreenWaves has sold over 300 GAPuino GAP8-based development boards with what it claims are “multiple customer designs in progress.”

Linus Torvalds has announced the release of Linux 5.0, the latest version of the Linux kernel, and once again it pulls in a range of improvements and new features for the RISC-V instruction set architecture (ISA).

Linux has boasted support for the open RISC-V ISA for a while, now, to the point where it’s possible to build a fully-functional desktop using off-the-shelf hardware. That doesn’t mean there isn’t still work to do, however, and the launch of the Linux 5.0 kernel brings with it a range of improvements highlighted by CNX Software.

For the RISC-V ISA, these improvements include improved support for RV64I-based RISC-V implementations, a fix for a bug which would see CPUs attempting to enter a sleep mode when the system should be shutting down, support for RV32I MODULE_SECTIONS, and a new architecture-agnostic SBI ‘earlycon’ driver. Other improvements include fixes to improve the auditability of Linux on RISC-V architectures.

Linux 5.0 doesn’t concentrate purely on RISC-V, of course: embedded developers will also be interested in the new features and improvements made on the proprietary Arm and recently-royalty-freed MIPS architectures – the former receiving, among other things, a new energy-aware scheduling (EAS) feature for Arm’s big.LITTLE asymmetric multiprocessing platforms and the latter the ability to build a kernel with zero floating point support for nanoMIPS compatibility.

The success, and continued development, of RISC-V in the Linux kernel is a heartening sign that adoption of the free and open source ISA is already healthy and growing – and it will be very interesting to see what the next couple of Linux releases bring. More information on Linux 5.0, meanwhile, can be found on the Linux Kernel Mailing List.

Olof Kindgren has announced the release of FuseSoC 1.9.1, and it brings with it improved documentation produced using the Sphinx Python Documentation Generator.

Having a useful end product should be the primary goal of all open-source projects, but it shouldn’t be viewed as the only goal: no matter how useful a tool may be, if it’s not usable it may as well not exist. Documentation is key to accessibility, and all-too-often overlooked – which is why Olof’s work to improve the documentation of FuseSoC, the package manager and build tool collection for hardware description language (HDL) projects, is to be lauded.

“Following the good example of other FOSSi [Free and Open Source Silicon] devs, I’m taking the opportunity today to release version 1.9.1 of FuseSoC,” Olof writes on his Twitter account. “A ‘position’ argument to generators and Sphinx docs would be the noteworthy changes this time.”

The new documentation, generated using the Sphinx documentation utility, is available now on Read the Docs. FuseSoC 1.9.1 itself can be installed or updated using the ‘pip’ package management tool: “pip install fusesoc”.

The Free and Open Source Silicon (FOSSi) Foundation has announced it has been selected once again to be a mentor organisation in the Google Summer of Code (GSoC) programme, and is looking for students to participate.

A not-for-profit organisation founded with the aim of promoting and assisting with the development and deployment of free and open source silicon solutions, the FOSSi Foundation’s participation in the Google Summer of Code programme will see it acting as a mentor organisation and umbrella covering a wide range of FOSSi designs, open source electronic design automation (EDA) tools, and related ecosystem projects.

“Google Summer of Code is an excellent programme for students to get a stipend by Google to work on open source projects,” explains FOSSi Foundation director Olof Kindgren. “Your job is to write a realistic project proposal to show us that you have a good idea of the work involved, and discuss the idea with us to get feedback. Our job is to match you up with a suitable mentor.

“As there are more student proposals than we have seats, a well-written project idea is important for us to judge whether we should choose you over someone else. It is also a good idea to get involved with the community early on to get a better feeling for what kind of project you want to do, and what already exists.”

As in previous years, the FOSSi Foundation has published a list of possible project ideas, though those outside the list are also welcome, along with details of how students can discuss and submit their proposals.

Finally, Google has announced it is bringing its Tensor Processing Unit (TPU) technology to external developers for the first time, launching a suite of development boards and accelerators for edge-processing under the Coral brand.

Google first announced the Tensor Processing Unit, an in-house custom silicon project to accelerate deep-learning compute performance in its servers, in May 2016; in July 2018 it announced the Edge TPU, a variant which drew considerably less power and was aimed at bringing AI acceleration to edge devices. At the time, the Edge TPU development board – a system-on-module (SOM) whose carrier board looks not unlike a Raspberry Pi in layout – was available only to those invited into the company’s alpha-testing programme, but now it has made them available to all under the new sub-brand Coral.

The Coral Edge TPU development board is exactly as previously unveiled: a SOM, also available without carrier board for embedding into finished products, featuring an NXP i.MX 8M quad-core Arm Cortex-A53 processor and Edge TPU co-processor alongside 1GB of LPDDR4 memory and 8GB of eMMC storage expandable via microSD. For those not looking to work on an entirely new hardware platform, it is joined by a new Coral Edge TPU Accelerator which connects to any Linux-based system – including, Google points out, the Raspberry Pi, albeit at reduced USB 2.0 speed – and provides the same co-processor technology.

Google has partnered with Mouser to supply the parts internationally, with the USB Accelerator priced at £73.19 and the development board at £151.75 (both prices inc. VAT). Full details are available on the official website.