Developer Clifford Wolf has announced the release of Yosys 0.8, the latest version of the popular open synthesis suite framework, bringing with it a range of new improvements and bug fixes.

Designed to ease register-transfer level (RTL) development, analysis, and formal verification for projects written in the Verilog hardware description language (HDL), Yosys – the Yosys Open Synthesis Suite – was first launched in 2012 as the first full-featured open-source package for Verilog HDL synthesis. Since its initial release, the tool has proven popular among developers looking to ease their synthesis work.

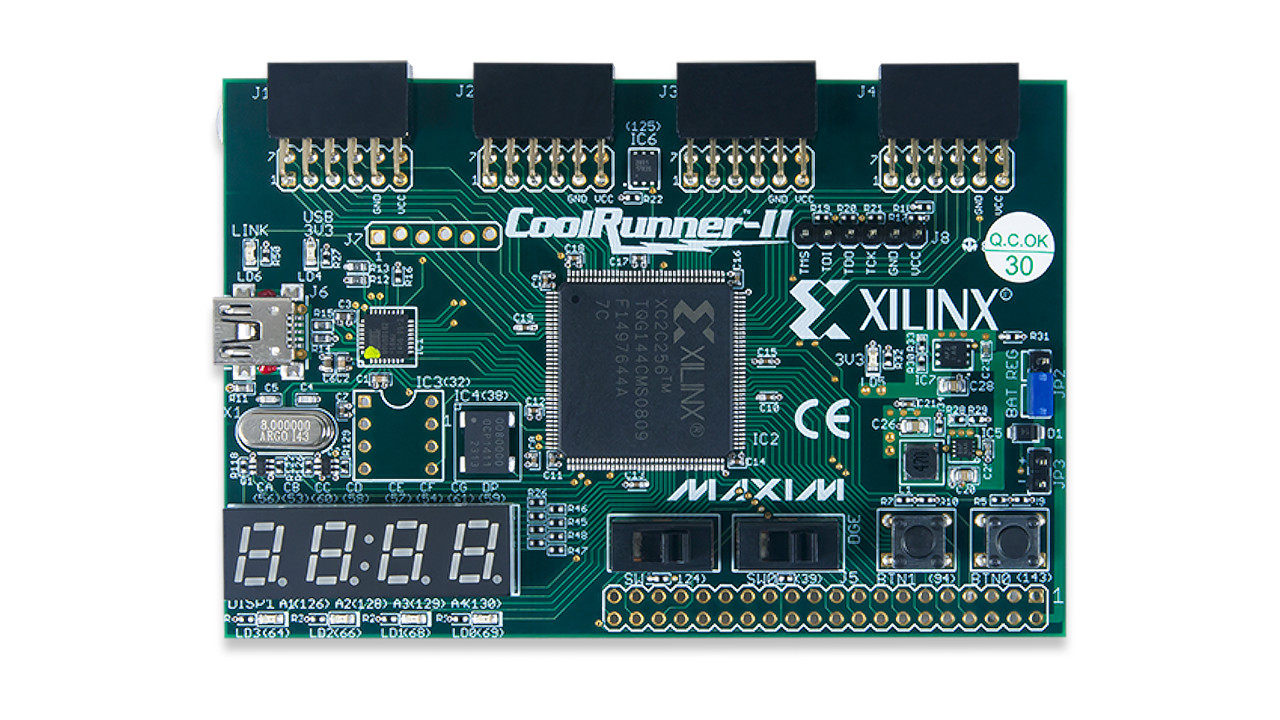

The freshly-released Yosys 0.8 brings with it a number of improvements and bug fixes, including a wide range of new commands, initial support for new circuit development platforms including the CoolRunner-II, eASIC, and ECP5, expanded iCE40, MAX10, and Cyclone IV support, and a number of enhancements to the Verific front-end.

Anyone currently using Yosys is advised to upgrade to Yosys 0.8, which is available to download now from the GitHub repository under the permissive ISC Licence.