Electronic Design is continuing its 11 Myths series, which covered LoRaWAN last month, with a look at the RISC-V open instruction set architecture (ISA).

“Many companies today are exploring free, open-source hardware and software as an alternative to closed, costly instruction set architectures (ISAs). RISC-V is a free, open, and extensible ISA that’s redefining the flexibility, scalability, extensibility, and modularity of chip designs. Despite its rich ecosystem and growing number of real-world implementations, there are misconceptions about RISC-V that have companies holding back from fully realising its benefits,” claims author Ted Marena, director of system-on-chip (SoC) and field-programmable gate array (FPGA) products at Microsemi Corporation, in his introduction to the piece.

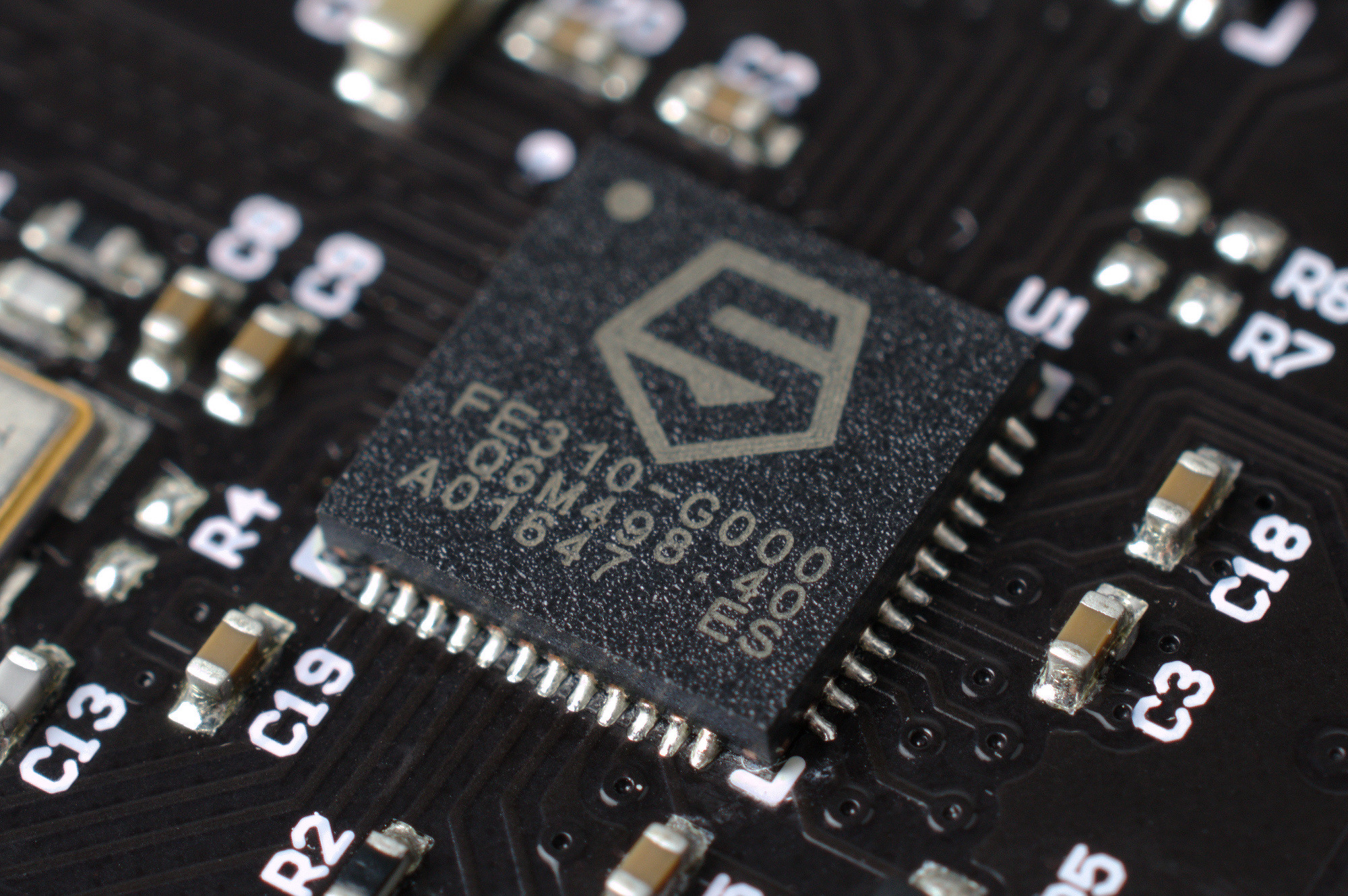

Ted’s article covers a range of common misunderstandings regarding RISC-V, ranging from the mistaken belief that RISC-V is a purely academic undertaking to the efficiency of implementations, licensing considerations, and the ability or otherwise to port designs from an FPGA to an application specific integrated circuit (ASIC) for mass production.

The full article can be read over on Electronic Design now.