The RISC-V Foundation, in partnership with Microchip Technology and Thales, has announced its second soft-core CPU competition – time time focusing on security.

Following on from its first soft-core CPU contest late last year, the RISC-V Foundation has announced its second. Where the first focused on performance and smart use of available resources, though, the second has a very different focus: security.

“With the proliferation of connected devices, security is one of the key challenges in hardware design. The free and open RISC-V ISA presents an incredible opportunity for the ecosystem to collaborate to develop more robust solutions for the growing security demands of today and the future,” explains Calista Redmond, chief executive of the RISC-V Foundation. “This contest is an opportunity for designers and hardware enthusiasts to rethink what is possible with computing design and build a secure RISC-V soft CPU that can prevent software security attacks.”

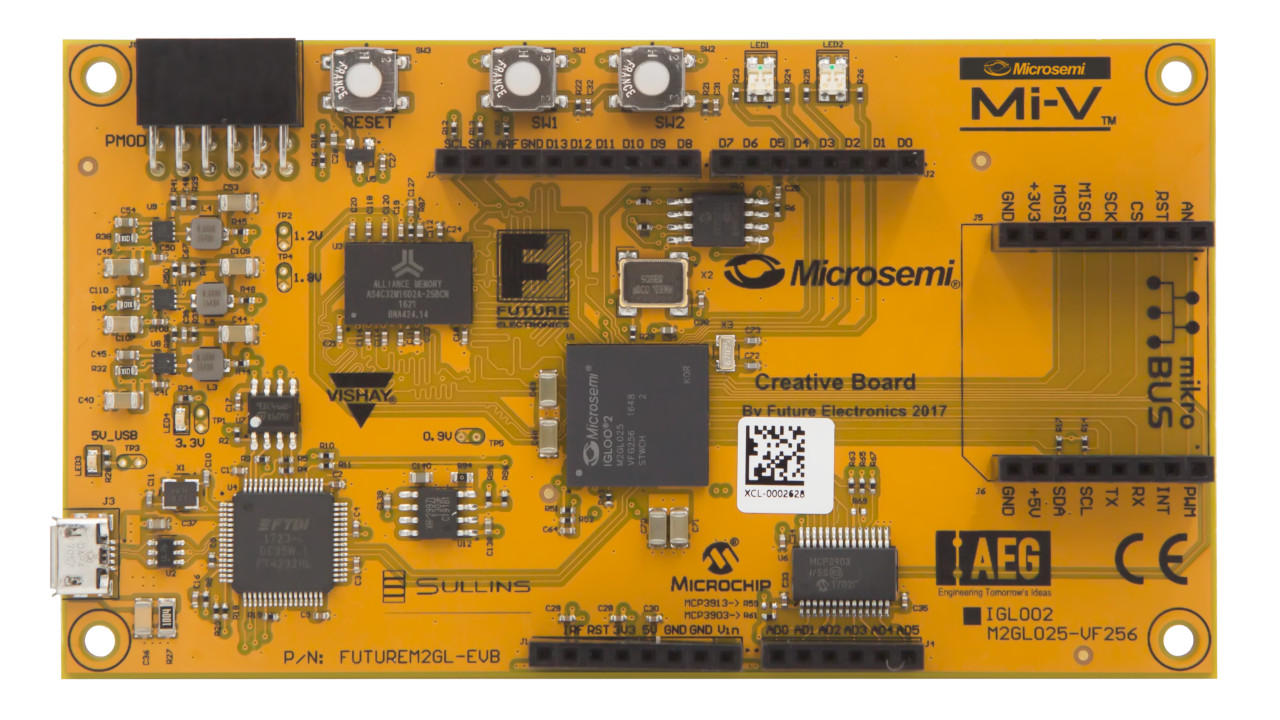

The contest, which targets Microchip’s Creative Development Board and its IGLOO 2 field-programmable gate array (FPGA), has three price levels: first place receives €5,000, a HiFive Unleashed development board, and an expansion board for same; second place receives €2,000 and a HiFive Unleashed board; and third place €1,000 and a HiFive Unleashed board. Entries will be judged on each design’s ability to resist five common attacks, total resource usage, expected power consumption, and points deducted for each change made to the compiler.

Interested parties can enter the competition on the RISC-V Foundation website. All entries must be written in Verilog, or a framework which generates Verilog as its output, and capable of running the Zephyr real-time operating system (RTOS) version 1.14. Entries need to be in by the 15th of September, and must be based on the RV32IMC ISA and have their sources publicly released.