Dover Microsystems’ Greg Sullivan has written of how Antmicro’s open-source Renode development framework has considerably decreased the length of his company’s design cycle – showcasing why the framework is becoming increasingly popular.

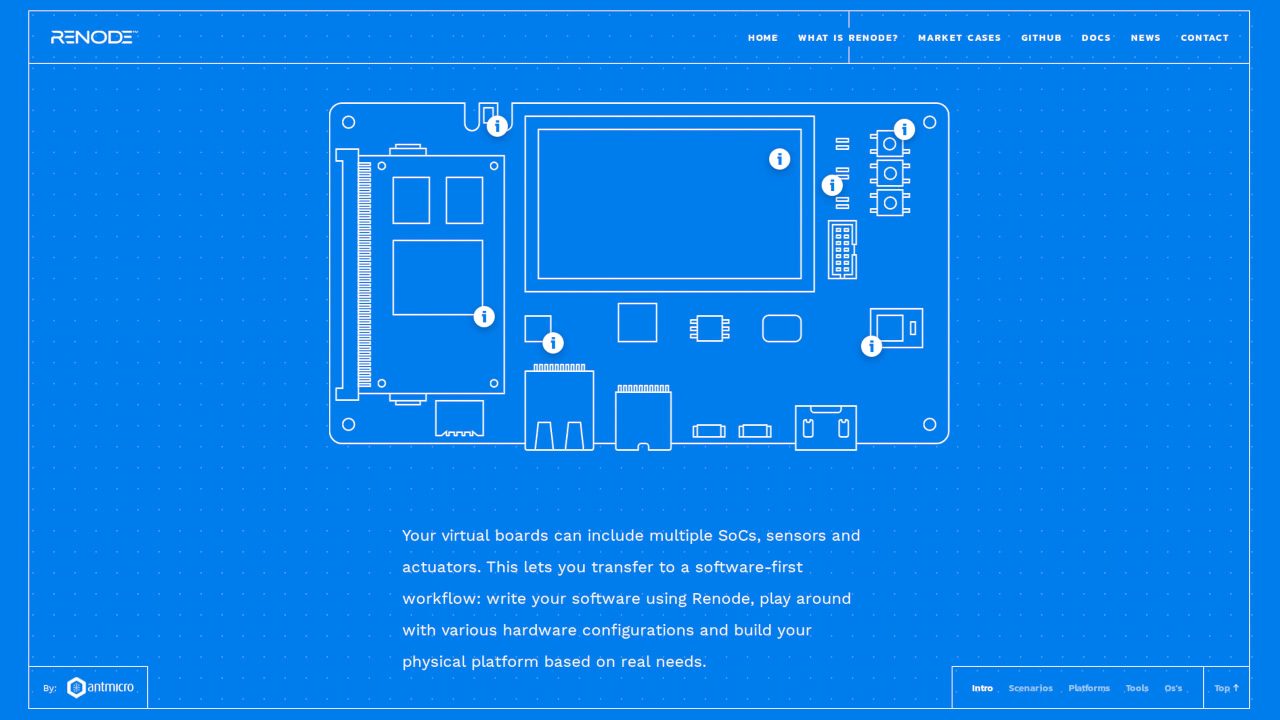

Built with embedded platforms and the Internet of Things (IoT) in mind, Renode allows for the execution, debugging, and testing of embedded software unmodified on a standard off-the-shelf PC, and is proving popular for those designing the hardware itself. Its three-layer design allows the creation of virtual system-on-chip parts from a series of building blocks – including those based on the open RISC-V instruction set architecture – then build the resulting virtual SoC into a virtual hardware device. Each simulation can also support multiple virtual boards over simulated wired or wireless connectivity, further extending the work that can be done before having to move to physical prototypes.

Example case studies published to the official website include Google’s use of Renode to test the TensorFlow Lite machine learning framework, support for the Microsemi PolarFire SoC, the use of Renode as a Zephyr development tool, and even a utilities provider which used Renode to develop hardware based on the EFR32 SoC.

Now, Dover Microsystems’ Greg Sullivan has written of how Renode is an integral part of his company’s hardware-software co-design efforts, and has directly led to a reduction in the design cycle length and the complexity of evaluating said designs.

“The Renode framework’s flexible nature, its open-source availability, and the existence of commercial support provided by its authors made it easy for Dover to first build a prototype implementation of their desired workflow and then contract Antmicro to implement (and release into the open-source domain) functionalities that made Renode even better suited for their use case, such as per-instruction execution,” Greg explains. “In particular, using Renode, Dover engineers are now able to: switch between Arm and RISC-V based integration efforts using the same setup; prototype SoCs (both reference/minimal and customer-defined) at different levels of detail/fidelity.

“The hardware and software teams collaborate on the hardware interface (which of course will continue to evolve). As the hardware team starts implementing blocks in SystemVerilog, the software team creates models of the new blocks in C#, the native language underlying Renode,” Greg continues, outlining the workflow in which Renode sits. “The software team is then able to write firmware that communicates with the new hardware interfaces, and test that software under Renode simulation. Eventually, the software is run on an FPGA emulator.

“It is critical that design teams able to explore a large range of possible hardware/software co-optimisation techniques and tradeoffs, without a large, serialised ‘first-hardware-then-software development process.’ A flexible software functional simulator such as Renode allows Dover engineers to collaborate across the hardware-software divide to find optimal trade-offs between hardware and software complexity, making it integral to their efforts.”

Greg’s full write-up, which was written in partnership with Antmicro’s Michael Gielda, can be found on All About Circuits now. More information on Renode, meanwhile, is available on the official website.