RISC-V specialist Bluespec Inc. has announced its second RISC-V processor design, Flute, which it is making available as basic cores ahead of future releases which will include additional instructions for Linux and FreeRTOS compatibility.

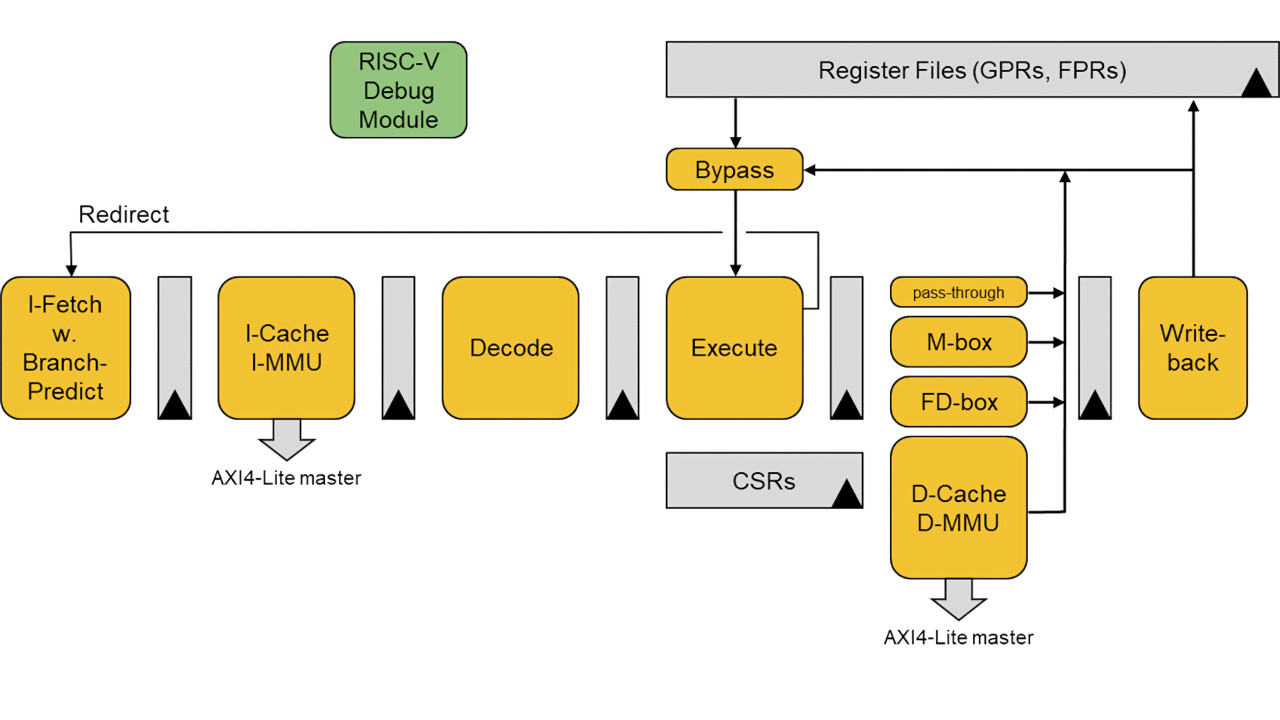

The follow-up to Bluespec’s existing Piccolo core, Flute is currently available in RV32IMU and RV64IMASU implementations with a floating-point and compressed-instruction variant supporting Linux and FreeRTOS operating systems to follow. The core uses a five-stage pipeline, can run at 100MHz on the Xilinx UltraScale field-programmable gate array (FPGA) platform using fewer than 5,000 look-up tables (LUTs), with 4KB instruction and data cashes and hardware multiply-divide.

“The availability of commercially-backed open-source processor cores is a unique RISC-V value proposition,” claims Rick O’Connor, executive director of the RISC-V Foundation, of Bluespec’s release. “With the emergence of the free and open RISC-V ISA an open-source business model is now possible for processor IP. This will certainly help RISC-V ignite a new era of hardware innovation, as Linux did for software.”

While only recently made available publicly, the Flute core has already found real-world uses: “We are using Bluespec’s Flute core as a fast and efficient way to take to market our Posit Numeric Unit IP,” explains Anantha Kinnal, co-founder and director of Calligo Technologies, an HPC and AI company based in Bangalore, India. “It provides us customization opportunities, an ability to focus on our value-added technology, and confidence to go to market with the necessary commercial support.”

The Flute core is available to download now in 32-bit and 64-bit variants, with Verilator and Icarus simulations, upon submission of the registration form on the official website.