Technology journalist Gareth Halfacree is running the AB Open Community Round-Up series, offering a fortnightly glimpse at what’s happening in and around open source hardware and software, wireless and related topics.

The fifth RISC-V workshop took place this week, and for fans of the open instruction set architecture (ISA) the news has been nothing but good. For those unable to attend the event, held at Google’s Quad Campus in Mountain View, California, Alex Bradbury has been doing a fantastic job summarising day one and day two over on the lowRISC blog while we’re pulling out a few highlights of our own below.

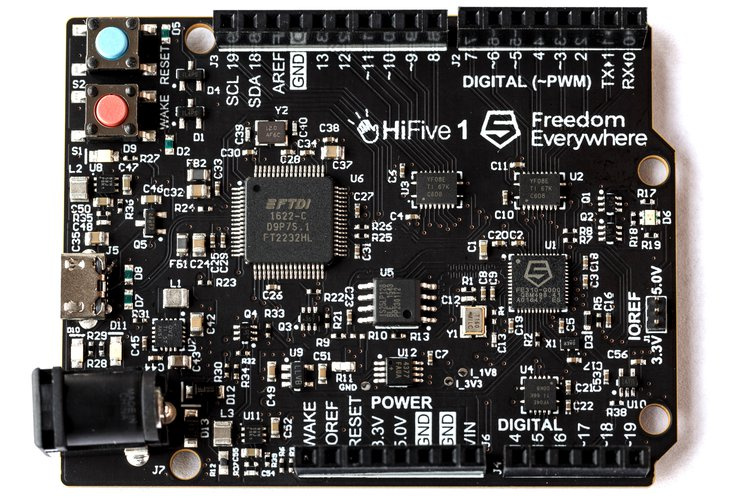

The biggest news for hobbyists was undoubtedly the announcement of the HiFive1 development kit from SiFive. Based on a microcontroller implementation of the RISC-V ISA dubbed the Freedom E310, the board follows the layout of the popular Arduino Uno – complete with, critics will despair to hear, the now-traditional irregular pin-header spacing, making it compatible with existing Arduino shields.

The HiFive1 boards are due to ship in volume early next year, priced at $59 (around £47 excluding taxes), with more information available on SiFive’s Crowd Supply campaign page. Those interested in the nitty-gritty of the Freedom RISC-V implementation, meanwhile, can view it in its entirety on the company’s GitHub repository.

SiFive isn’t alone in offering a complete crowdfunded RISC-V development board, though: rival OnChip has a competing campaign to produce its Open-V RISC-V microcontroller. With a more generous launch schedule that sees the first parts shipping in April 2018, OnChip is offering bare open-V chips for $49 or complete development boards for $99 (around £39 and £78 respectively, excluding taxes).

The company has also pledged long-term support, promising to keep the Open-V in production “for as long as there is demand” following its initial run of 70,000 chips. Its Crowd Supply campaign page has many more details.

On a more industrial-scale note, four companies have announced a partnership to launch a fully-integrated development platform for RISC-V Internet of Things (IoT) projects. BaySand, Codasip, Codeplay, and UltraSoC jointly announced their partnership at the RISC-V Workshop, promising to each bring something to the stack as a means of speeding product development: BaySand provides foundational IP and its Metal Configurable Standard Cell (MCSC) FPGA-like technology, Codasip provides a RISC-V implementation dubbed Codix-Bk, Codeplay’s ComputeSuite package provides development tools, while UltraSoC offers an on-chip debug and analytics architecture.

All four companies pointed to increased interest from customers in RISC-V, particularly for future low-power applications, and have promised that the stack can drop development time from anything up to 78 weeks for an application specific integrated circuit (ASIC) to 10 weeks for a BaySand MCSC version.

Away from single-core IoT-centric implementations, a special mention must also be given to Quan Nguyen and his team from the Massachusetts Institute of Technology (MIT) for a presentation on a prototype of a thousand-core RISC-V system.

Built around a new cache coherency protocol dubbed Tardis, the T-1000 prototype – named for the liquid metal enemy in Terminator 2: Judgement Day – connects FPGA-based RISC-V cores in a three dimensional mesh to prove its capabilities at scaling to many-core implementations. Quan’s presentation can be downloaded from the RISC-V website now.

#mc_embed_signup{background:#fff; clear:left; font:14px Helvetica,Arial,sans-serif; width:100%;}

/* Add your own MailChimp form style overrides in your site stylesheet or in this style block.

We recommend moving this block and the preceding CSS link to the HEAD of your HTML file. */